Bridge the gap between TSV and traditional WLFO/FOWLP

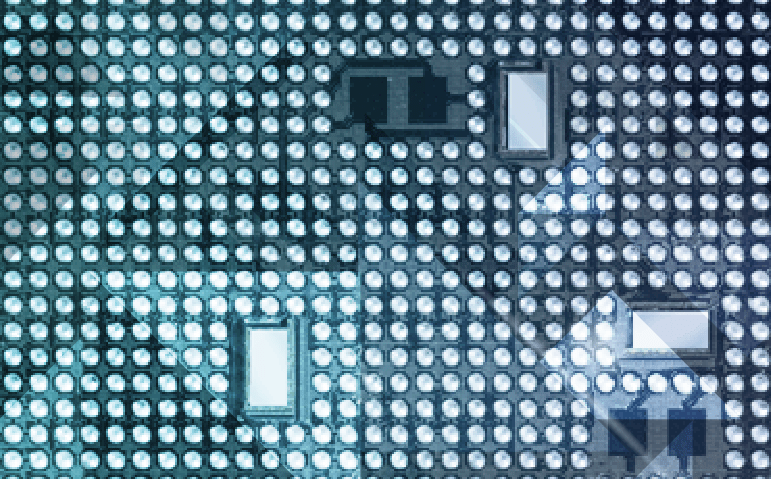

Our award-winning Silicon Wafer Integrated Fan-out Technology (SWIFT®/HDFO) technology is designed to provide increased I/O and circuit density within a reduced footprint and profile for single and multi-die applications.

SWIFT® technology enables the creation of advanced 3D structures, addressing the need for increased IC integration in emerging mobile and networking applications. The distinctive characteristics of SWIFT® are due, in part, to the fine feature capabilities associated with this innovative wafer level packaging technique. This allows aggressive design rules to be applied, compared to traditional WLFO and laminate-based assemblies.

Unique SWIFT® features include:

- Polymer dielectrics

- Multi-die and large die capability

- Large body package capability

- Interconnect density down to 2/2 μm

- Cu pillar die interconnect down to 30 μm pitch

- 3D/Package-on-Package capability utilizing Through Mold Via (TMV®) or tall Cu pillars

- Meets JEDEC MSL2a and MSL3 CLR and BLR requirements

Enabling Technologies For SWIFT® Packaging:

Key assembly technologies enable the creation of these distinctive SWIFT® features. Using stepper photo imaging equipment, 2/2 μm line/space features can be achieved, enabling very high-density die-to-die connections required for SoC partitioning and networking applications where 2.5D TSV would typically be used. Fine-pitch die micro bumps provide a high-density interconnect for advanced products, such as application processors and baseband devices. In addition, tall Cu pillars enable a high-density vertical interface for mounting advanced memory devices on the top of the SWIFT® structure.

Questions?

Contact an Amkor expert by clicking the request info button below.