Bridge the gap between TSV and traditional WLFO/FOWLP

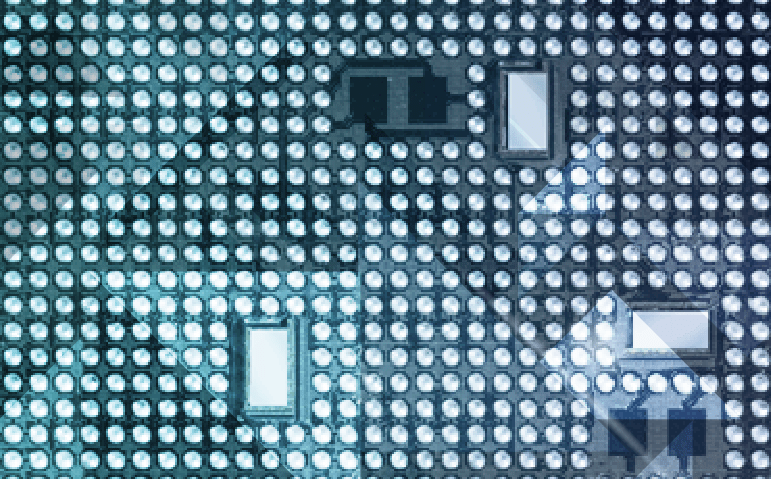

当社の Silicon Wafer Integrated Fan-out Technology(SWIFT®/HDFO)は、シングルおよびマルチチップのパッケージにおいてフットプリントとプロファイルを低減しながら、I/Oと回路密度の向上を実現します。

SWIFT®のユニークな機能には次のものが含まれます:

- ポリマー絶縁層

- マルチチップ、大型チップ対応

- 大型パッケージに対応

- インターコネクト密度:2/2μmまで対応

- Cuピラーチップ接続:30 μmピッチ対応

- スルーモールドビア(TMV®)または高さのあるCuピラーを利用した3D/パッケージ・オン・パッケージ対応

- JEDEC MSL2a、MSL3 CLR、BLR適合

SWIFT®パッケージングを実現する技術:

主要な組立技術により、この特色あるSWIFT®パッケージの製造が可能となります。ステッパー装置を使用することで、2/2 μmライン/スペースが実現でき、通常2.5DのTSVが使用されるSoCパーティショニングおよびネットワーク機器に求められる高密度のチップ間接続が可能になります。ファインピッチチップのマイクロバンプは、アプリケーションプロセッサやベースバンド機器などの先端製品向けに高密度接続を提供します。さらに、高さのあるCuピラーが、SWIFT®最上部に高度なメモリを実装するための高密度積層インターフェイスを可能にします。

ご質問やお問合せはこちらまで

以下の「リクエスト」をクリックしてご連絡ください