SWIFT® 的特色包括:

- 聚合物电介质

- 多晶粒和大晶粒封装

- 大尺寸封装能力

- 互连密度缩小至 2/2 μm

- 铜柱晶片互连缩小至 30 微米间距

- 3D/层叠封装功能采用穿塑通孔 (TMV®) 或高铜柱

- 符合 JEDEC MSL2a、MSL3 CLR 和 BLR 要求

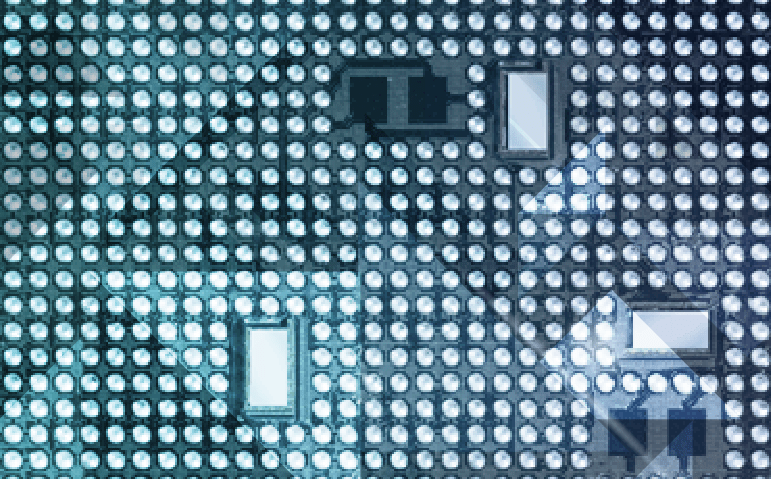

SWIFT® 封装的促成技术

关键封装技术让此类独特的 SWIFT® 功能成为可能。通过步进式成像设备实现 2/2 微米间距,以及 SoC 划分和网络应用中的极高密度晶片连接,此类芯片通常会采用 2.5D TSV。小间距晶片微凸块为先进产品提供高密度互连,例如,处理器和基带设备等。除此以外,高铜柱实现高密度垂直接口,以便于在 SWIFT® 结构顶部贴装先进的储存器设备。

有问题?

点击下方的 “获取信息“ 按钮,

联系 Amkor 专业人士。