增加封装的导电密度

宽带隙 (WBG) 半导体技术对功率封装带来了新的挑战和机遇。开发包括碳化硅 (SiC) 和氮化镓 (GaN) 在内的技术,比硅 MOSFET 具有更高的品质因数 (FOM),而且扩展了对功率电子产品的效率、输出功率和/或开关频率范围,以及操作温度范围。

由于功耗降低,特定尺寸功率器件可以控制更高电力负荷。例如,相对于硅基系统,采用氮化镓功率晶体管的电源系统在尺寸、重量和效率损失方面都只有前者的 ¼。氮化镓技术可以克服由无线系统等低功率 (50W) 端到中功率端,甚至高功率水平所带来的系统挑战。对 5G 系统的兼容性使其能够完美适应精密的中低功率封装。类似地,SIC 的功率控制能力高于硅基 MOSFET,而且对很多应用都有先进封装要求。WBG 器件的好处与优势需要新的封装选项,来最大限度地挖掘出整个电源系统的价值。

目前的离散功率封装受限于夹片、焊线和焊点的电气性能。一般来说,离散封装遵循着更大尺寸/体积和更强功率处理能力之间相互关联的设计理念。不过,此类更高效的晶体管技术提供在相同尺寸的封装中处理更高功率的能力,或者能够大幅减小其外观规格。

为了最大限度提高传统功率封装的总传导率,晶片设计的源极和漏极需要在 100% 或接近 100% 的可用空间中连接到电流承载材料。在传统上,通过增加电线数量、电线直径或者将固定到源极或漏极的夹片尺寸最大化可以实现这一点。

要彻底优化功率空间的功能性,必须促成三件事情。首先,源极和漏极的总传导率需要被最大化。其次,热和电接面需要被取消,或在相当程度上减小其长度/厚度。第三,需要增加封装的传导材料密度。在下图中,我们检视了当今所使用的大量功率专用型封装的传导密度。

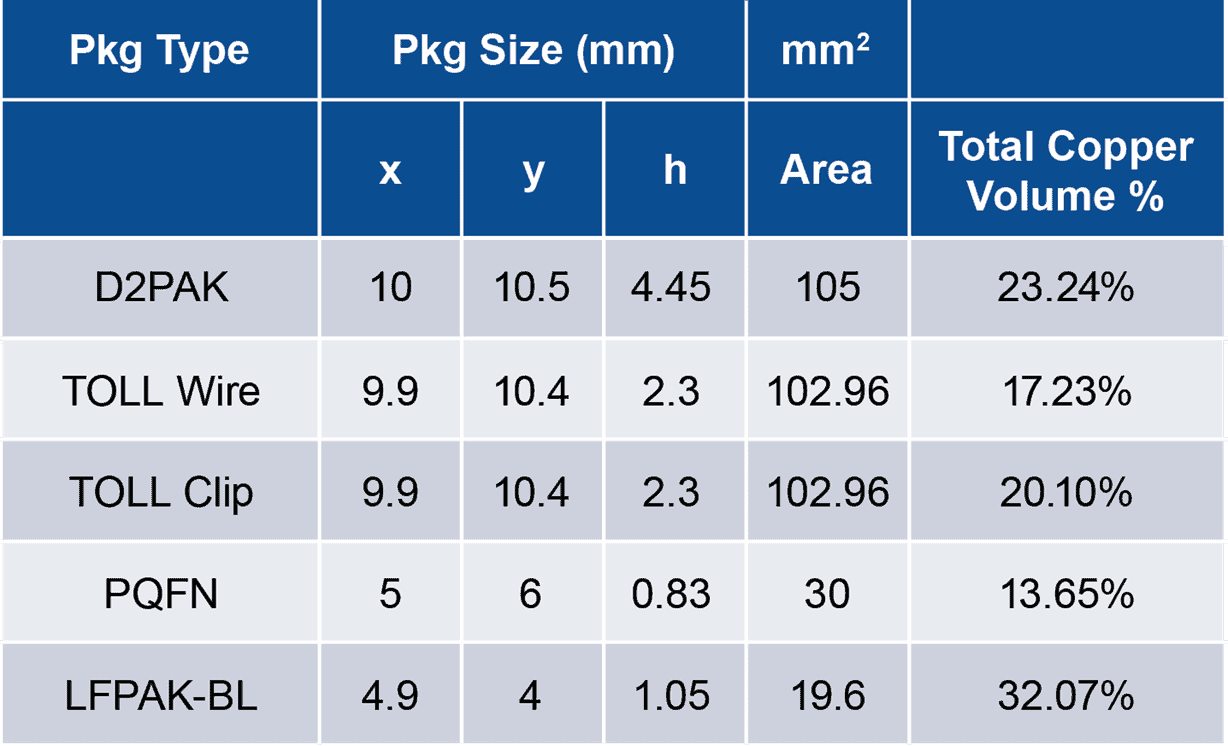

表 1. 现有功率封装的比较数据。

要在最大程度上优化热和电属性,封装体积内最好尽量采用更多传导材料。在当前的大多数功率封装中,封装所使用的传导材料很少超过 25%(见表 1)。

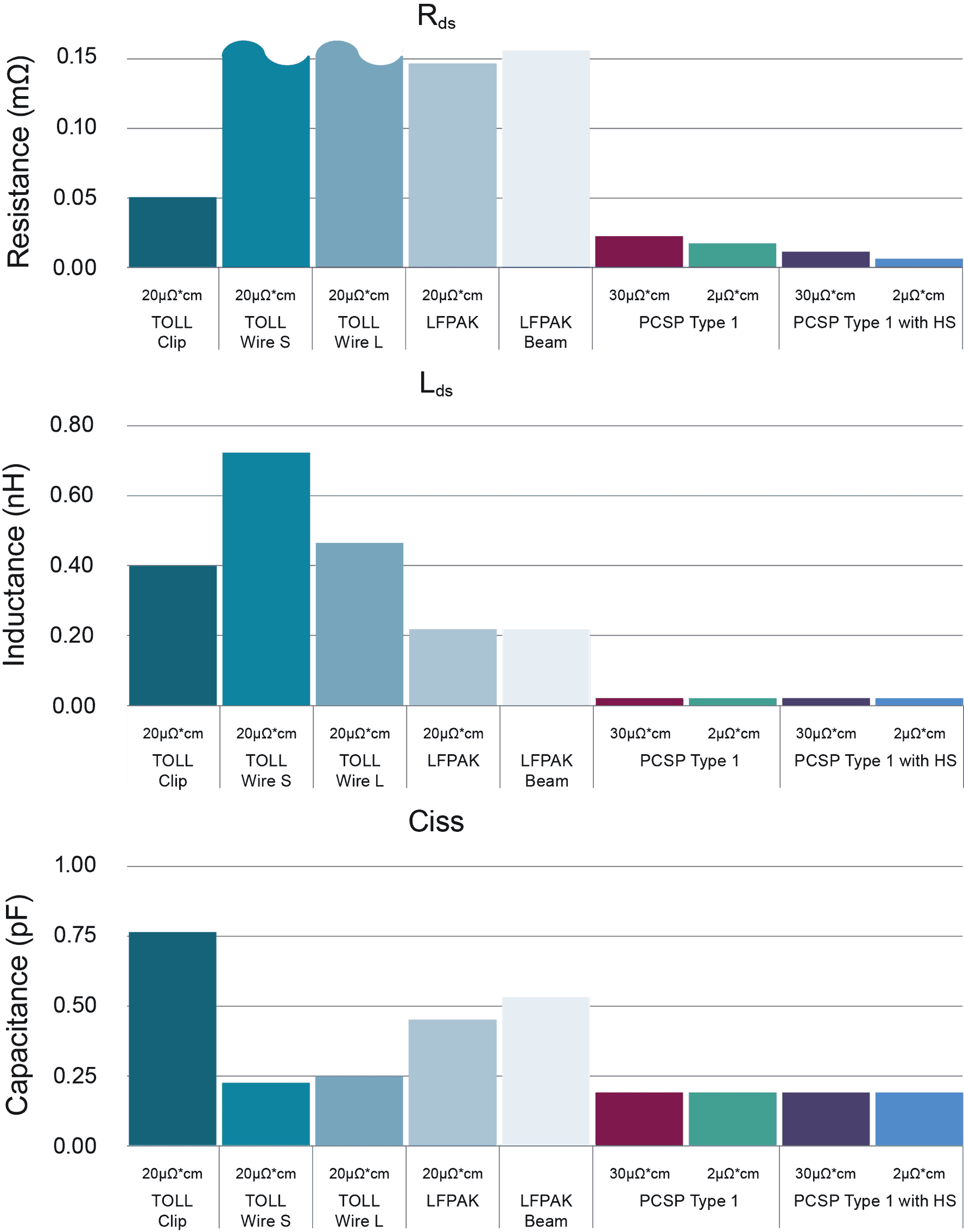

我们需要新的封装格式来将封装中的传导密度最大化。由 Amkor 开发的 PowerCSP™ 技术就是其中的概念之一。PowerCSP 技术的一般传导密度在 40-70% 之间,因此其外观规格可以比传统功率封装小得多。传导密度的增加要归功于持续使用铜基板而不是夹片或焊线。

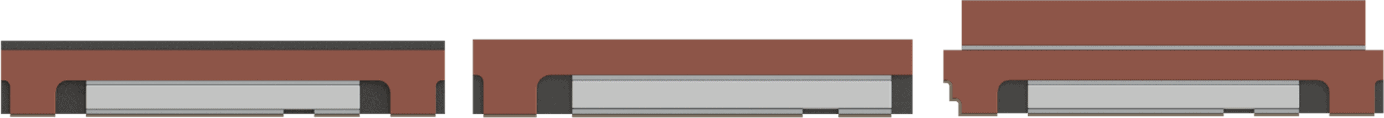

图 2. 实施 PowerCSP™ 技术显示了它的灵活性,以及众多结构选项。

图 2. 实施 PowerCSP™ 技术显示了它的灵活性,以及众多结构选项。

在 PowerCSP 技术中,其设计通过同时充当载流和散热元件的铜焊盘直接连接晶片,使晶片能够使用全部可用的源极和漏极区域。相较之下,它降低了封装的电阻和电感。封装的总传导密度发挥作用,而为源极和漏极使用全部界面也在最大限度降低了系统中的可能损耗。

图 3. 适用于 PowerCSP™ (PCSP) 的 RDS、LDS 及 Ciss 和不同版本 TOLL 及 LFPAK 封装的模拟比较。

行业可能专门为功率封装开发其他封装概念,但封装的传导密度将是关键因素。无论是 Si、GaN 或 SiC,它们都可以因为封装的传导密度增加而获益,包括电阻和电感的减小,以及最终缩小封装的外观规格。增加封装传导密度的努力只能帮助解决封装的总体功率密度问题,并利用 Si 和 WBG 器件所能提供的全部优点。

关于作者

Shaun Bowers 是 Amkor Technology, Inc. 常驻在亚利桑那州坦佩的主流先进封装集成副总监。他于 2000 年加入 Amkor,目前负责汽车、引线框架和功率封装业务部门的封装开发。他过去还担任过技术项目管理、销售和客户服务等职务。在加入 Amkor 前,他曾在 Johnson Matthey Electronics 和 Honeywell Electronic Materials 就职。他持有贡萨格大学的机械工程学位。