利用 S-SWIFT™ 技术革新 IC 封装

扇出式技术与基板的结合

在不断发展的集成电路技术领域,对高性能设备的需求急剧增加,尤其是在人工智能、高性能计算和数据中心领域。新冠肺炎疫情进一步加快了这一需求的增长,把硅技术的极限推向了新的边界。Amkor 的 S-SWIFT™ 是一种开创性的封装解决方案,旨在应对这些挑战并彻底改变集成电路封装行业。

对先进封装解决方案的需求

随着业界不断推进硅技术节点的最小化(目前已达到 3 纳米),相关的成本和开发时间也随之大幅增加。节点尺寸越小,出现缺陷的风险就越大,最终导致晶圆产量下降。小芯片技术已经成为克服这些限制的有效方案,它能够将核心块分解成更小的芯片,这样既能提升晶圆的良品率,也能降低设计成本。然而,要实现这些异构块晶粒之间的互连,就需要用到先进的 IC 封装技术。

IC 封装的发展

传统上,多芯片模块 (MCM) 倒装芯片球栅阵列 (FCBGA) 封装已用于层压基板上的多芯片异构接口。然而,由于基板的电气路径较长,这种方法不适合先进节点 IC。2.5D 硅通孔 (TSV) 技术的引入提供了更短的电气路径,但在高频应用中受到性能问题的限制。这导致了高密度扇出型 (HDFO) 接口技术的发展,该技术避免了使用硅和无机电介质,转而采用了有机电介质。

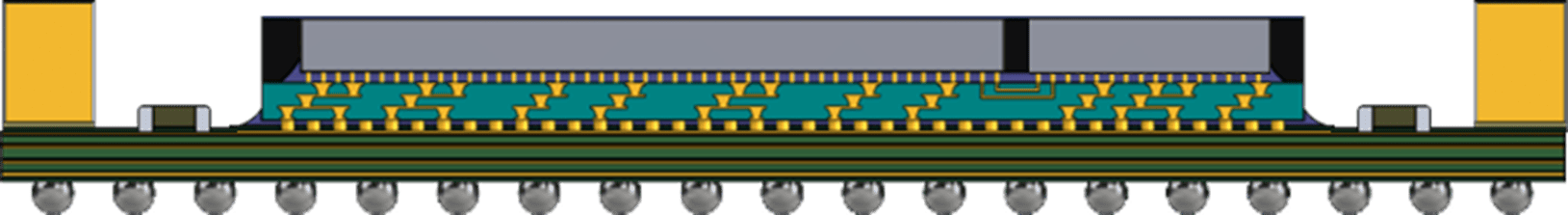

S-SWIFT:游戏规则改变者

Amkor Technology 的 S-SWIFT(基板硅晶圆集成扇出式技术)封装在 HDFO 领域脱颖而出。它提供了更高的带宽和晶粒间互连,可与高密度介质层进行异构集成。S-SWIFT 方法解决了几个关键的设计问题,包括细节距、μ-bump 接口、热组装期间的精确翘曲控制、毛细管底部填充、包覆成型技术和模具侧凸块工艺。

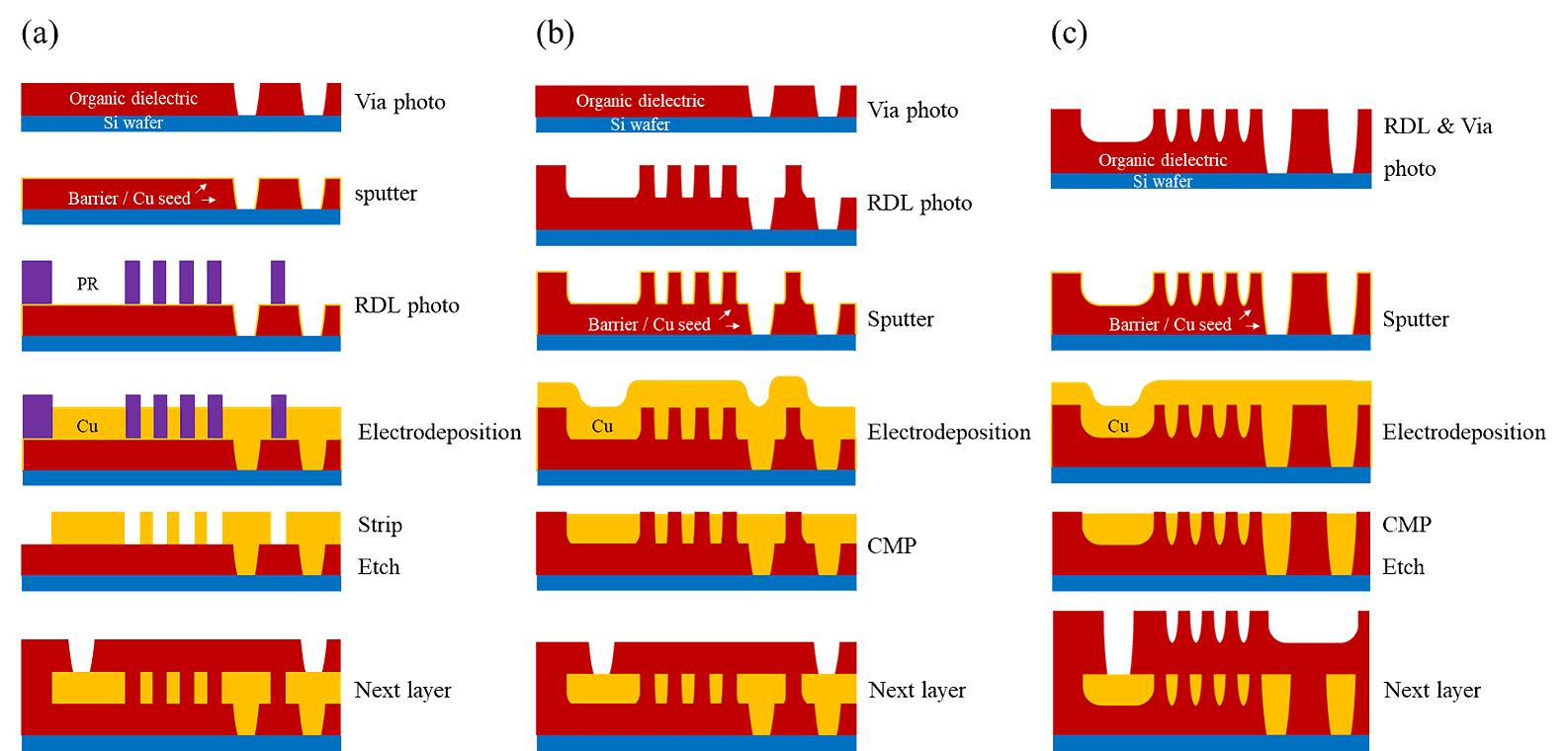

S-SWIFT 的核心技术之一是高密度再布线层 (RDL) 技术。在 HDFO 封装中,RDL 提供芯片到芯片的接口,而更高密度的 RDL 对于将芯片与更小节点大小的块互连至关重要。半加成工艺 (SAP) 一直是 RDL 制造的主流技术,但它在定义小节距特征方面面临挑战。为了克服这些问题,有人提出了一种采用有机电介质的双层工艺,将 RDL 嵌入有机电介质中,以防止籽晶层底切问题。

图 1:S-SWIFT™

內埋式线路 RDL (ETR) 工艺

內埋式线路 RDL (ETR) 工艺是 RDL 制造领域的一项重大进步。无需蚀刻工艺就能将线路埋入电介质层,解决诸如籽晶层底切和侧壁蚀刻问题等挑战。ETR 工艺中的双层铜 (Cu) 结构在高频信号通过特性方面具有优势,因为光滑的铜表面受电子散射的影响较小。

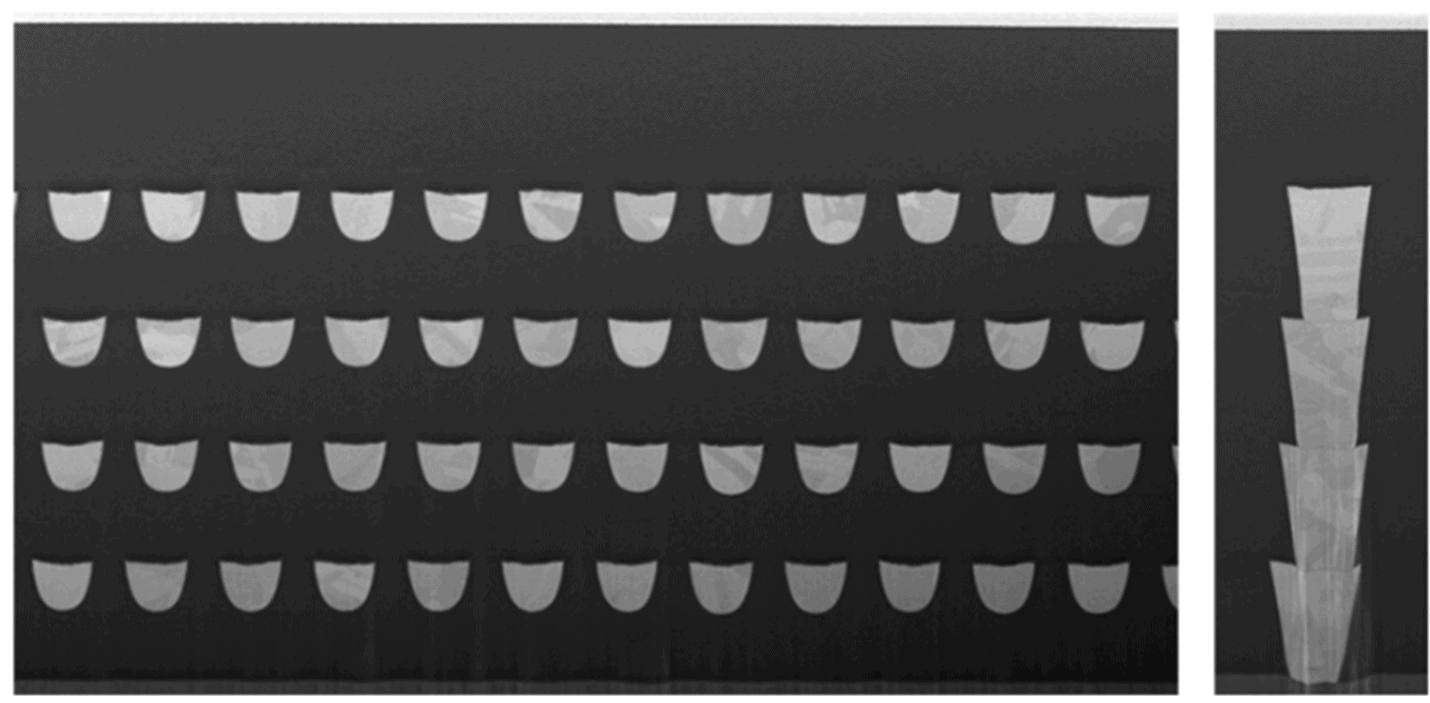

ETR 还简化了 RDL 制造工艺,与当前的双层法相比,制程步骤减少了 40%,与 SAP 相比,制程步骤减少了 33%。制程步骤的减少意味着成本降低和效率提高。ETR 工艺已展现出优异的图案化能力,可实现 2/1 μm 线宽/线距和各种通孔尺寸的沟槽图案。

图 2:(a) 半加成工艺 (SAP)、(b) 双层工艺和 (c) 新型內埋式线路 RDL 工艺的 RDL 工艺流程原理图。

图 3:通过 ETR 工艺形成的 4 层 RDL 的横截面图像,线宽/线距为 2/1 μm,堆叠通孔为 2 μm

可靠性和性能

S-SWIFT 封装中的 ETR 结构的可靠性已经过全面测试。环绕 ETR 三个面的籽晶层起着屏障的作用,可防止铜离子迁移,确保在电流、热量和湿度条件下的可靠性。采用 ETR 的 S-SWIFT 封装已通过行业标准可靠性测试,包括湿浸、温度循环、无偏高加速应力测试和高温存储测试。

结论

Amkor Technology 的 S-SWIFT 封装采用內埋式线路 RDL,代表着 IC 封装技术的重大飞跃。通过解决传统封装方法的局限性并提供可靠、高性能的解决方案,S-SWIFT 可满足人工智能、高性能计算和数据中心应用日益增长的需求。随着业界不断推动硅技术的发展,S-SWIFT 等创新技术将在塑造高性能计算的未来方面发挥至关重要的作用。要了解更多信息,请访问 Amkor.com/s-swift