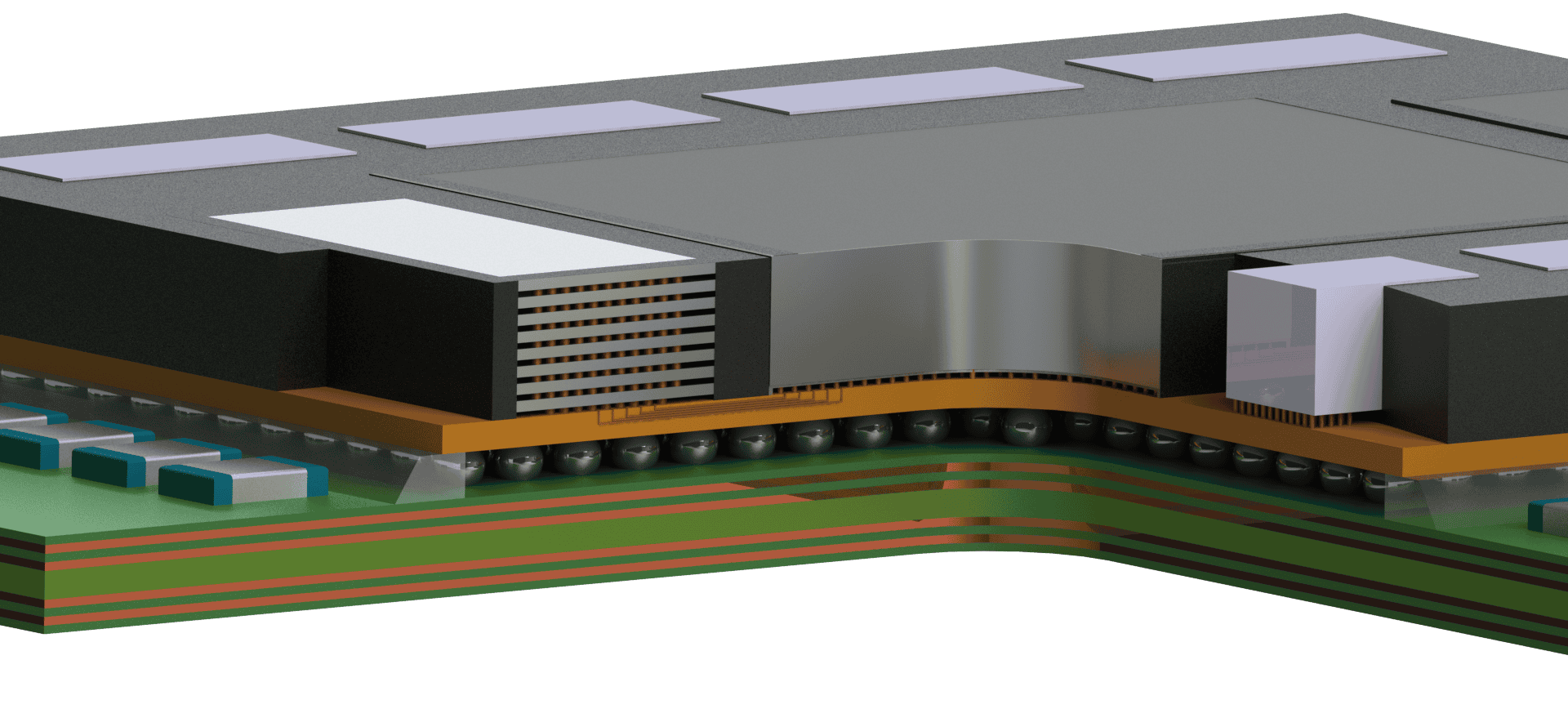

S-SWIFT 是一种革命性的新型封装技术

基板-SWIFT(S-SWIFT)技术,也称为(基板上)硅晶圆集成扇出式技术,正在彻底改变先进封装领域。S-SWIFT 技术通过提高 I/O 和电路密度,同时缩小尺寸与外形,成为单晶粒和多晶粒应用的首选解决方案,完美满足移动和网络设备对更高 IC 集成度日益增长的需求。

S-SWIFT 改变了异构 IC 封装领域的游戏规则,实现多个小芯片和存储器的高性能、低成本集成。该技术不仅增加了 I/O 和电路密度,而且为先进的 3D 结构发展铺平了道路,使其成为下一代移动和网络应用中不可或缺的组成部分。S-SWIFT 技术非常适合需要大封装尺寸和高 I/O 密度 (>1000) 的应用。

扇出式技术与基板的结合

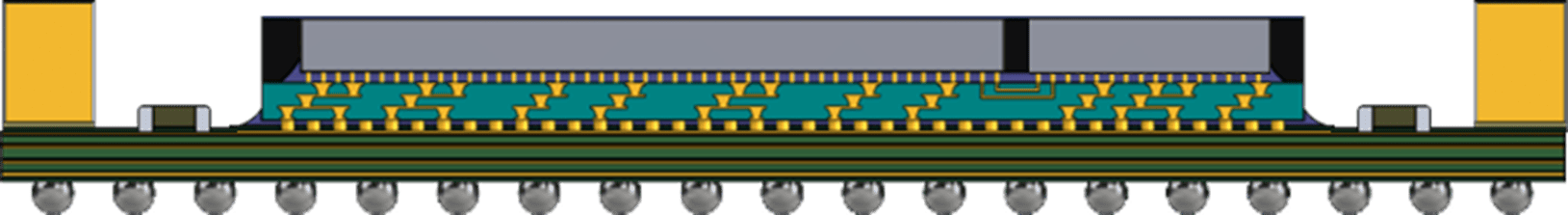

S-SWIFT 是 2.5D TSV 的创新替代品,是一种扇出式封装,可提高芯片性能并降低成本。S-SWIFT 通过将芯片倒装到高引脚数的球栅阵列 (BGA) 基板上,并结合再布线层 (RDL) 实现更短的晶粒间 (D2D) 互连,将整个扇出式封装视为单晶粒。然后将此智能设计安装到 BGA 基板上,为传统 2.5D 硅通孔 (TSV) 技术提供一种经济高效的替代方案。

S-SWIFT 的一个重要特性是 RDL,它能实现多个芯片之间更短的 D2D 互连。该设计将整个扇出式封装视为单晶粒,然后安装到 BGA 基板。通过集成这些先进功能,S-SWIFT 提供了一种比传统 2.5D TSV 技术更经济高效的替代方案。

封装结构

- 安装在高引脚数 BGA 基板上的扇出式封装倒装芯片

- RDL 有助于缩短多个芯片之间的 D2D 互连

芯片集成

- 在单个封装内集成多个小芯片

- 小芯片可以是不同的功能单元,例如 ASIC 或 HBM

无介质层设计

- 无需介质层,降低了复杂性和成本

电气性能

- 由于 D2D 连接较短,因此具有出色的电气性能

- 插入损耗更小、阻抗控制更好、翘曲度更低

高 I/O 密度

- 支持高 I/O 数量 (>1000)

- 非常适合大尺寸封装和网络/服务器应用

- 高成本效益:无需介质层,降低了封装成本

- 电气性能:提供更好的阻抗控制、更低的插入损耗和更低的翘曲度,从而提高电气性能

- 高 I/O 数量:支持超过 1000 个 I/O 的封装,非常适合网络和服务器应用

- 上市时间:利用现有的扇出/倒装芯片技术,该技术可缩短上市时间

与 2.5D 相比,S-SWIFT™ 技术成本更低、封装更薄、插入损耗更小、阻抗控制更好、翘曲度更低,从而具有卓越的电气性能。这些优势使 S-SWIFT 成为相关应用的理想选择。

关键应用包括:

- 高性能计算 (HPC):通过高效实现关键互连,增强高性能计算应用能力

- 网络和服务器应用:高 I/O 密度使 S-SWIFT 成为满足网络和服务器需求的理想选择

- 人工智能 (AI):卓越的电气性能和高速、低延迟的芯片间互连,非常适合需要大量内存和计算能力的 AI 应用

- ASIC 和 HBM:S-SWIFT 的芯片后置技术适用于封装 ASIC 和 HBM

有问题?

点击下方的 “获取信息“ 按钮,

联系 Amkor 专业人士。