TSV와 WLFO/FOWLP 간의 차이 연결

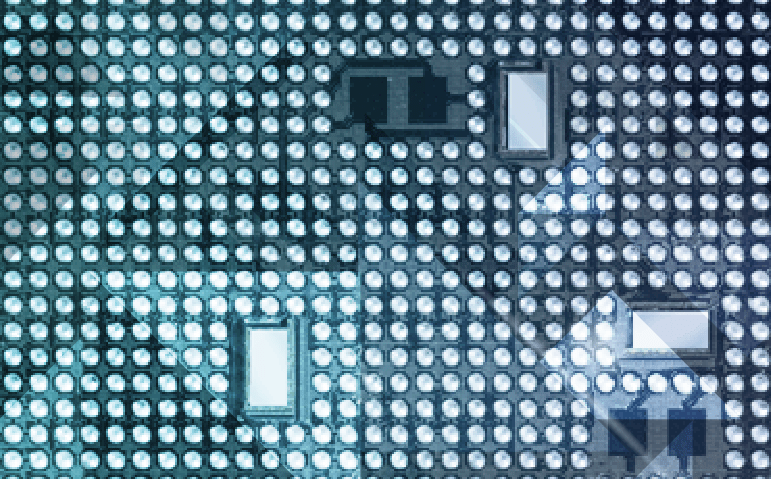

당사의 Silicon Wafer Integrated Fan-out Technology (SWIFT®/HDFO) 기술은 더 적은 공간을 차지하며 I/O와 회로 집적도를 높여 한 개 혹은 그 이상의 칩을 사용하는 어플리케이션에 적합한, 업계 수상 이력이 있는 기술입니다.

SWIFT®만의 고유한 특징

- 폴리머 유전체

- Multi-die and large die 가능

- 대형 패키지 지원

- 인터커넥트 밀도 2/2 μm로 감소

- 최소 30μm 간격의 Cu pillar die 인터커넥트

- Mold Via (TMV®) 또는 tall Cu pillars를 활용하는 3D/Package-on-Package 기능

- JEDEC MSL2a, MSL3 CLR, BLR 요건 충족

SWIFT® 패키징을 구현하는 기술

SWIFT®의 독자적인 특징은 핵심 어셈블리 기술이 있기에 구현될 수 있습니다. 스테퍼 포토 이미징 장비를 사용하면 2/2 μm 라인/스페이스를 구현해서, 2.5D TSV가 주로 사용되는 SoC 파티셔닝 및 네트워킹 애플리케이션에 필요한 초고밀도 다이 투 다이 연결이 가능해 집니다. 미세 피치 다이 마이크로 범프는 애플리케이션 프로세서(AP)와 베이스밴드 장치 같은 고급 제품에 들어가는 고밀도 인터커넥트를 제공합니다. 또한 키가 큰 구리 돌기를 사용하면, SWIFT® 구조 상단에 첨단 메모리 장치를 실장할 수 있는 고밀도 수직 인터페이스를 만들 수 있습니다.

Q & A

앰코에 대해 궁금한 점이 있다면

하단의 ‘문의하기’를 클릭하세요.