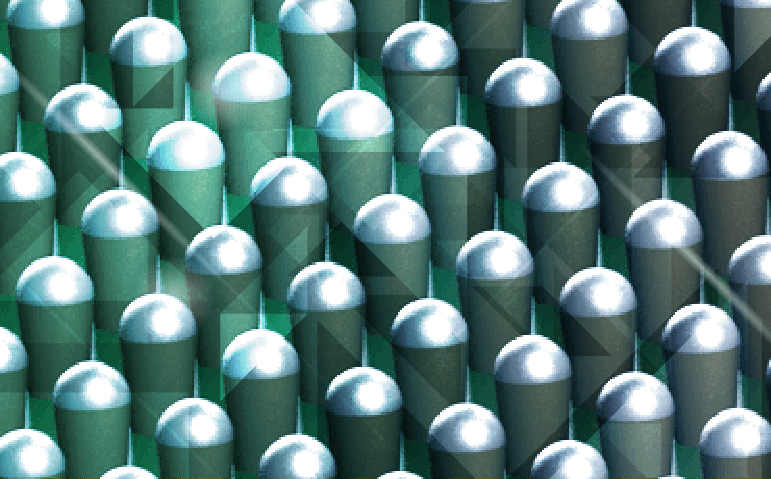

높은 밀도, 신뢰성 및 성능을 위한 차세대 범프 기술

Copper Pillar 범프는 현재와 앞으로 요구될 RoHS 조건을 만족하면서 다양한 설계에서 이점을 제공하는 Flip Chip 접합에 사용되고 있습니다. 트랜시버, 임베디드 프로세서, 애플리케이션 프로세서, 전원 관리, 베이스밴드, ASIC, SOC 등 미세 피치, RoHS/친환경 조건 준수, 저렴한 비용, 일렉트로마이그레이션 성능의 조합을 요구하는 애플리케이션에 적합한 접합 방법입니다

Benefits of Copper Pillar

- 미세 피치와 관련 최소 30 µm의 인라인 및 30/60 µm의 스태거드(Staggered) 가능

- 고전류 애플리케이션을 위한 우수한 일렉트로마이그레이션 성능

- Cu 필러 범프 전 웨이퍼 레벨에서의 전기적 테스트

- 와이어본드 용으로 설계된 칩의 본드 패드 오프닝/피치 및 패드 금속화와 호환 Flip Chip으로의 변환이 용이하기 때문에 신속한 시장 진입이 가능

- 기판 층 수를 줄임으로써 설계 단계에서의 비용 절감

- 고밀도 범프 설계에 Au 스터드 범프에 비해 저렴한 비용의 미세 피치 Flip chip (FPFC) 접합

- Cu 바 타입, 표준 Cu Pillar, 미세 피치 Cu Pillar 및 마이크로 범프 등 다양한 Cu Pillar 라인업 애플리케이션의 요구사항에 따라 Cu+Ni+무연, Cu+Ni+Cu+무연 등 다양한 스택업에도 대응

- Repassivation 유/무에 대응

- 첨단 실리콘 노드 Low-k 장치에 적합

- 칩과 패키지의 거리를 좁혀 더 작은 풋프린트를 제공하는 언더필의 필렛 크기 축소

- TSV 및 CoC용 최대 30μm 초미세 피치

Q & A

앰코에 대해 궁금한 점이 있다면

하단의 ‘문의하기’를 클릭하세요.