휘어짐 관리 개선 및 무결점을 위한 패키지

휴대전화, 디지털카메라, 게임 및 기타 모바일 애플리케이션과 같은 휴대용 전자제품은 PoP(Package-on-Package) 제품군이 제공하는 적층형 패키지와 작은 사이즈라는 이점을 얻을 수 있습니다.

앰코는 미래의 선두주자로서 PoP 실장 면적과 패키지 두께를 감소시킨 고밀도 적층 사양과 같은 차세대 PoP 패키지 요구사항을 충족시키기 위해, 심도 있는 개발과 생산 능력을 유지하는 데 전념하고 있습니다.

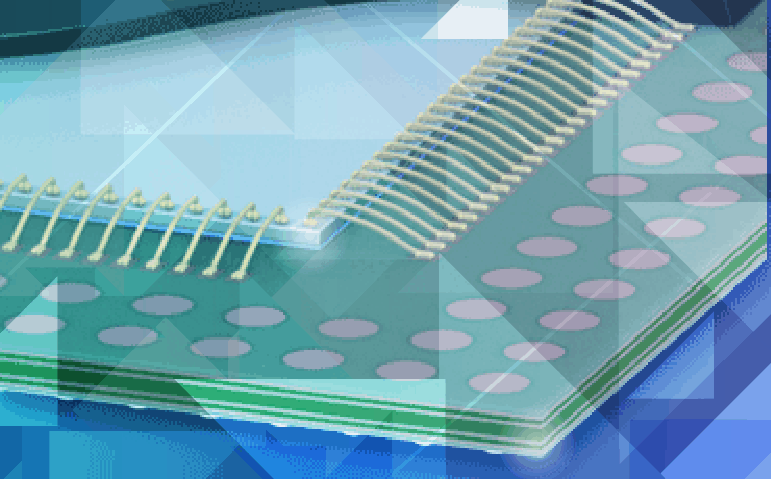

Package Stackable Very Thin Fine Pitch BGA (PSvfBGA), 2004년부터 생산을 시작하여, 테스트 및 SMT 처리로 flip chip 패키지의 휘어짐을 방지하고 무결점을 실현하고자 wire bond 또는 hybrid (flip chip plus wirebond)로 single 및 stacked die를 지원하고 있습니다.

Package Stackable Flip Chip CSP (PSfcCSP)는 exposed die 형태의 bottom 패키지를 사용할 수 있고, 당사 PSFcCSP 패키지의 fcCSP 어셈블리 과정에 PSvfBGA 패키지의 적층 설계 기능이 접목되어있습니다. PSfcCSP는 0.5 mm pitch의 fine pitch stacked interface이 가능하도록 얇게 노출된 flip chip die를 보유하고 있으며, 이는 센터 몰드를 하는 PSvfBGA의 도전 과제입니다.

Through Mold Via Package-on-Package (TMV® PoP) bottom 패키지의 몰드 영역을 관통하여 접합되는 차세대 PoP 솔루션입니다. TMV는 얇은 substrate와 패키지 대비 큰 사이즈의 die가 사용되어 안정적인 bottom 패키지를 제공합니다. TMV 구조가 적용된 PoP는 단일, stacked die 또는 flip chip 설계를 지원할 수 있습니다. 이 기술은 0.4 mm pitch의 저전력 DDR2 메모리 사양의 요구사항에서 이상적인 솔루션이며 0.3 mm pitch 또는 그 이하의 solder ball pitch로도 적층 사양을 확장할 수 있습니다.

Q & A

앰코에 대해 궁금한 점이 있다면

하단의 ‘문의하기’를 클릭하세요.