턴키 WLCSP 제품에 대한 업계의 수요 충족

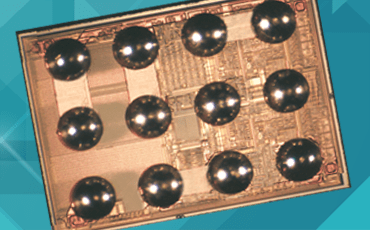

앰코는 디바이스와 최종 제품의 마더보드를 솔더로 직접 연결하는 WLCSP (Wafer Level Chip Scale Packaging)를 제공합니다. WLCSP 풀 턴키 솔루션을 위해 웨이퍼 범핑 (패드 재배선 포함/제외), 웨이퍼 레벨 파이널 테스트 (프로브), 디바이스 싱귤레이션, 테이프 & 릴 패킹을 지원합니다.

다이 상부 PBO 또는 폴리이미드(PI) 절연체 위에 형성된 앰코의 견고한 UBM(Under Bump Metallurgy)은 가혹한 조건의 보드 레벨을 충족하는 안정적인 상호연결 솔루션을 제공합니다.

WLCSP 패키지 제품군은 고사양의 RF WLAN 콤보 칩에서부터 FPGA, 전원 관리, Flash/EEPROM, 통합형 수동 네트워크 및 표준 아날로그에 이르기까지 다양한 반도체 디바이스에 광범위하게 적용될 수 있습니다. WLCSP는 시장에서 가장 작은 폼팩터와 고성능, 최고의 신뢰성을 만족시키는 반도체 패키지 플랫폼을 활용하여 고품질의 반도체 제품을 저비용으로 제공할 수 있습니다.

앰코는 세 가지 WLCSP 옵션을 제공합니다.

- CSPnl Bump on Repassivation (BoR) 옵션은 재배선이 불필요한

기기에 안정적이고 비용 효율적인

실제 칩 크기 패키지를 제공합니다.

BoR 옵션은 우수한 전기적/기계적 특성을 가진 Repassivation 폴리머 층을 활용합니다. UBM이 추가되고 솔더 범프가 다이 I/O 패드 바로 위에 배치됩니다. CSPnl의 표면실장

어셈블리 및 리플로우 기술은 업계 표준에 따라 설계되었습니다.

- CSPnl Bump on Redistribution (RDL) 옵션 은 도금된 구리 재배선층(RDL)을 추가하고 I/O 패드를 JEDEC/EIAJ 표준 피치로 라우팅하여 CSP 애플리케이션에 사용된 기존

디자인 그대로 사용 가능합니다.

폴리이미드 또는 PBO와 같은 유전체층과 니켈 기반 또는 두꺼운 Cu로 형성된 UBM은 최고 수준의 보드

레벨 신뢰성을 보장합니다. 재배선된 CSPnl는 산업표준 표면 실장 어셈블리 및 리플로우 기술을 활용하며, 검증된 디바이스 크기 및 I/O 레이아웃에는 언더필 공정이 필요하지 않습니다.

- CSPn3 옵션은 단층 구리 UBM과

재배선(RDL)을 활용하며, 이 단순화된 프로세스는 비용 및 사이클 타임을 20% 이상 줄입니다. CSPn3 은 2009년부터 생산 중이며, 도입 이후 40억 개 이상의 제품이 출하되었습니다.

Q & A

앰코에 대해 궁금한 점이 있다면

하단의 ‘문의하기’를 클릭하세요.