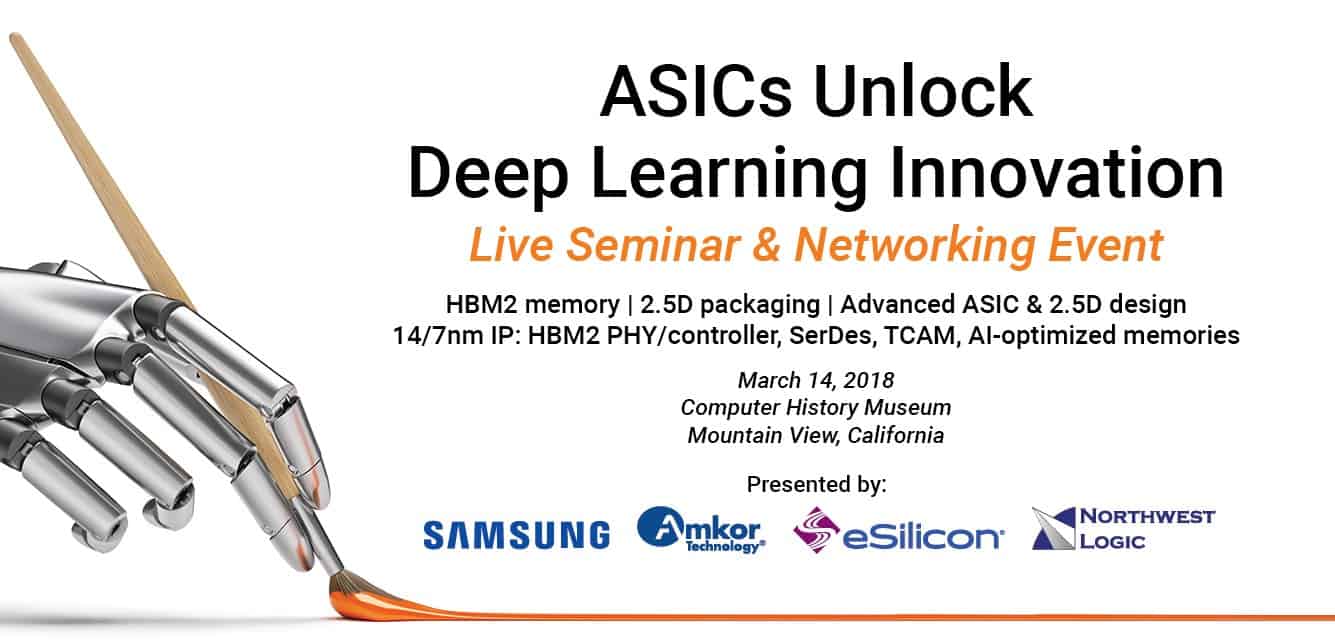

ASICs Unlock Deep Learning Innovation: Live Seminar in Silicon Valley

Practical implementation of deep learning technology demands extreme performance, low power and efficient access to massive amounts of data. Advanced application-specific integrated circuits (ASICs) play a critical role in the path to production for innovations that involve deep learning. In fact, many AI-related applications cannot be realized without the performance and security that a custom chip provides.

Practical implementation of deep learning technology demands extreme performance, low power and efficient access to massive amounts of data. Advanced application-specific integrated circuits (ASICs) play a critical role in the path to production for innovations that involve deep learning. In fact, many AI-related applications cannot be realized without the performance and security that a custom chip provides.

Moreover, an implementation platform is needed that supports high-bandwidth memory (HBM2), 2.5D system-in-package (SiP) design and implementation, HBM2 controllers, HBM2 PHY and memory IP designed for deep learning, all supporting 14nm and 7nm FinFET process nodes that address the challenges of deep learning.

Please join Samsung Electronics, Amkor Technology, eSilicon Corporation and Northwest Logic as we explore a complete implementation platform for deep learning ASICs.

There is no charge to attend this deep learning seminar and networking event. However, advance registration is required.

Wednesday, March 14, 2018

3:30PM – 7:30PM

Computer History Museum

Mountain View, California

Presentation Focuses

- Samsung Electronics: HBM2 memory solutions

- Amkor Technology: Advanced packaging solutions

- eSilicon: ASIC/2.5D design and enabling 7/14nm IP platforms (HBM2 PHY, SerDes, TCAM, custom memories)

- Northwest Logic: HBM controller

A networking reception (wine, beer, light food and “lucky draw” prizes) will follow the presentations.