DSMBGAの熱シミュレーションと大型HDFOの熱機械結合シミュレーション

電子パッケージングは、デバイス数の増加、高密度化、異種デバイス集積(HI)が進み、より複雑になってきています。モバイル分野では、かつてはプリント基板(PCB)上の個別部品だったシステムが、関連する受動素子やインターコネクトとともに、システム・イン・パッケージ(SiP)スタイルの単一サブアセンブリに移されています。ハイパワーコンピューティングやデータセンターのパッケージでも同様の傾向が見られ、メモリはインターポーザベースの単一集積パッケージに移行しています。最新の高度なパッケージの急速な発展と複雑化とは対照的に、機械的応力と熱伝達を支配する物理法則は不変です。近年、パッケージング材料の開発は大きな進歩を遂げましたが、機械的応力や熱の問題を解消する革新的な材料は存在しません。

パッケージ設計時のエンジニアリング上の意思決定を導くために、機械的(構造的および熱的)シミュレーションは、デバイスの性能予測、デバイスの不具合調査、根本原因の調査、最適化調査の実施に適したツールです。このブログ記事では、高いシミュレーション精度が要求される複雑なパッケージ特有の課題に焦点を当て、シミュレーションを使用してパッケージの熱性能の特性を明らかにした2つのケーススタディについて紹介します。

ケーススタディ1:モバイル市場向けパッケージング

最初のケーススタディは、システム・イン・パッケージデバイスがモバイル市場向けである場合についてです。パッケージは、積み重ねられた2つのプリント基板(PCB)の間に挟まれるため、パッケージから熱を除去するために利用できるオプションが制限されます。例えば、熱除去のために熱をPCBに伝導させる必要がありますが、パッケージ全体の厚さが限られているため、上面に銅製のヒートスプレッダの設置は出来ないといったことです。

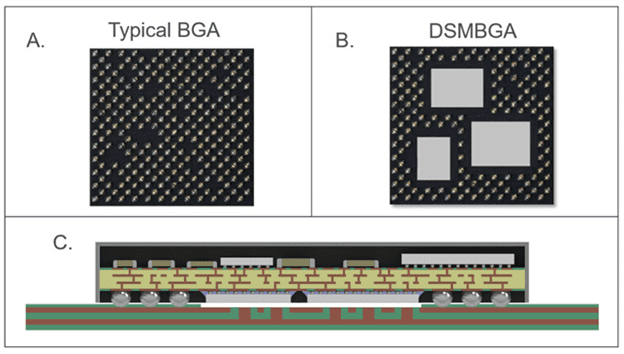

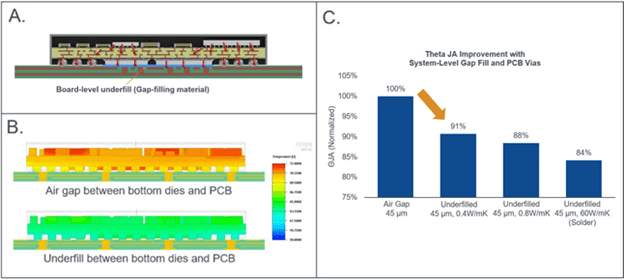

そこで、両面成形ボールグリッドアレイ(DSMBGA)において、高熱伝導性エポキシ樹脂成形材料(EMC)、BGAを大型銅(Cu)ポストに変更、下面露出チップとPCBの隙間を塞ぐシステムレベルのアンダーフィル(図1参照)などの改良を試みたところ、システムレベルのアンダーフィルだけが、JEDEC標準の静止空気環境において、ジャンクションから周囲への熱抵抗(ΘJA)を約10%低減し、大幅な熱改善を実現しました。Cuポストの改善はごくわずかで、高熱伝導性EMCの改善は1%未満でした(図2参照)。このシミュレーションは、シーメンス社のSimcenter Flothermを使用して行われました。

図1:レイアウトの違い

(A)標準的なBGAデバイス (B)サブストレートの底面にアクティブコンポーネントとチップを備えたDSMBGAデバイス (C)DSBGAデバイスの代表的な断面

図 2:(A)サブストレート下側のチップの下にある基板レベルのアンダーフィルの位置 (B)アンダーフィルされていないパッケージ(上)とアンダーフィルされたパッケージ(下)の温度差シミュレーション。カラースケールは画像間で統一 (C)各種アンダーフィル熱伝導率のシミュレーション結果グラフ

ケーススタディ2:大型ボディパッケージ

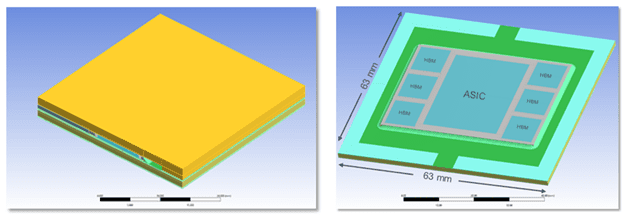

2つめのケーススタディは、中央の特定用途向け集積回路(ASIC)と複数の高帯域幅メモリ(HBM)モジュールを備えた大型ボディの高密度ファンアウト(HDFO)パッケージの構造と熱の連成シミュレーションです(図3参照)。ほとんどの熱シミュレーションでは、(速度と簡略化のために)ASIC/HBMモジュールの上部と蓋の下部の間の熱界面材料(TIM)接着線の厚さが一定であると仮定しています。この調査では、ASICおよびモジュール領域全体の接着線の(反りによる)厚さの変動がパッケージの熱性能にどのように影響するかをよりよく理解することが目的でした。

図3:大型HDFOモデル

(左)4分の1対称図 (右)ASIC+6HBM HDFOモジュールを示すために蓋を隠した拡大図

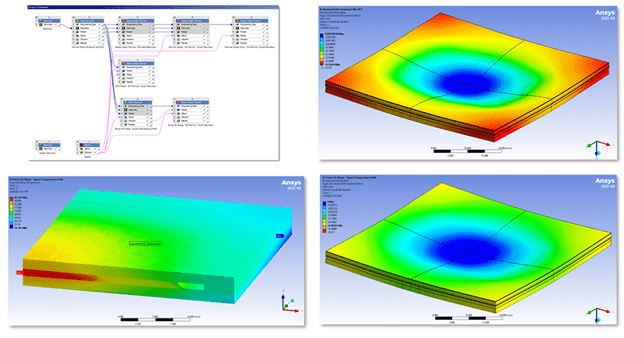

63x63mmのHDFOパッケージは、最初にAnsys Icepakでシミュレートされ、Ansys Workbench Mechanicalの構造に適用できる「パワーオン」温度プロファイルを生成しました。この温度プロファイルには2つの目的がありました。1つ目は、構造モデル全体に温度条件を適用して応力を作み出し、各材料の異なる熱膨張係数によるモデルの変形を計算することです。2つ目は、蓋の上部とサブストレートの下部の温度境界条件を計算して、変形形状とさまざまなTIM接着線のAnsys Mechanical定常熱シミュレーションに適用することです(図4参照)。

図 4:(左上)Ansysプロジェクトの回路図 ※熱モデルと構造モデルを結合するサブシステムのリンクを図示

図 4:(左上)Ansysプロジェクトの回路図 ※熱モデルと構造モデルを結合するサブシステムのリンクを図示

(右上)パッケージの反り、20℃、デッドバグビュー(サブストレート底面を見ている状態)

(右下)「電源投入時」の温度勾配を適用したパッケージの反りにデッドバグビューを適用

(左下)Icepakからインポートした温度プロファイル境界条件

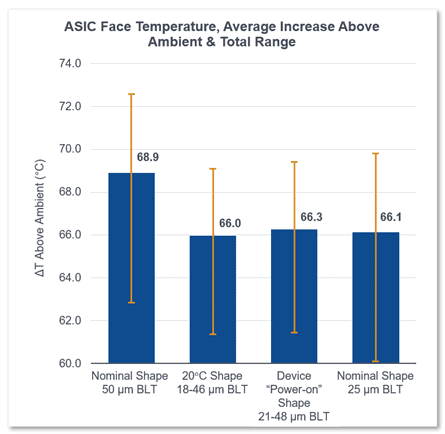

次に、変形形状(室温での反りベースラインの20°Cと、Icepakでシミュレートされた「電源投入時」の温度の両方で計算)を、熱モデルの形状として使用しました。未変形のベースラインに対して測定されたアクティブ表面接合部温度の変動を計算し、チップ表面全体で報告しました(図5参照)。

図 5:ASIC温度の温度結果グラフ ※エラーバーは、チップフェイス全体の全温度範囲を表示

結論

Ansysの機械的熱モデルでは、チップ面全体の平均ASIC温度が88.9℃、最大92.6℃、最小82.8℃(チップ全体の温度差は9.7℃)になったと報告されています。20°Cの形状モデルでは、平均チップ温度が86.0°C、最大89.1°C、最小81.4°C(チップ全体の温度差は7.7°C)と報告されています。「電源投入時」の形状モデルでは、平均チップ温度が86.3°C、最大89.4°C、最小81.4°C(チップ全体の温度差は8.0°C)と報告されています。

接着線の厚さ(BLT)のばらつきを考慮したモデルのチップ温度は、モジュール中央の接着線が薄く、モジュール角の接着線が厚いため、より一貫性があり、チップ全体で差が少ないように見えます(50μm BLTのベースラインとの比較)。このケーススタディで将来モデルの不確実性をよりよく理解することができました。

著者

Nathan Whitchurchは、Amkorでパッケージングとメカニカルシミュレーションをサポートするシニアスタッフエンジニアです。エレクトロニクスパッケージング分野に参入する前は、車載コンピューターラックエンクロージャ、電波熱設計、データセンターの熱分析、システム統合などのプロジェクトに携わっていました。パッケージレベルでのメカニカルシミュレーションについて、システムレベルの情報と知識を提供しています。南カリフォルニア大学で機械工学の学士号を取得しています。