ヘテロジニアスICパッケージング:パフォーマンスとコストの最適化

主要な集積回路(IC)ファウンドリでは、すでに7nmおよび5nmウェハを出荷しており、3nm製品についても、その認定が進行中です。トランジスタの密度が高くなると、それらの製造プロセスは従来以上に高価となり、従ってウェハのコストも高騰し続けています。新しいノードの登場時に、欠陥の密度が比較的横ばいであったとしても、シリコンの単位面積当たりのコストは非線形に増加します。こういった経済的理由から、将来の製品アーキテクチャに関しては、新らたなパッケージング技術の議論が真剣に交わされています。

パフォーマンスが最優先される場合、新しいシリコンノードの実用的アプリケーションにおいて許容が可能な、トランジスタ密度とクロック速度が検討されます。このことは、最新のシリコンノードに配置してもパフォーマンスを向上させることのない、他の従来型高性能チップの領域に、どのような影響を与えているでしょうか?

ヘテロジニアス・パッケージングは業界の答えであり、長い間究極の理想とされてきましたが、最近になってようやく設計のアプローチが実用化されました。シングルチップのシステム・オン・チップ(SoC)であったものの一部は、ホモジニアス設計から切り出され、より小さな独立シリコンチップで作成されるようになりました。メモリと通信する入出力I/Oブロックの削減や、長距離シリアライザー/デシリアライザー(SerDes)タイプについて検討することも最初のトレンドとなりました。

これにより、電気的、機能的、物理的なビルディングブロックのランドスケープが作成され、IC機能ブロックを調整して何度も再利用できるようになりました。このように、元の投資をより多くのエンドデバイスに分散させることは、ほんの数年前には考えられないことでした。

半導体業界は、2.5Dシリコン貫通ビア(TSV)製品でこの最新の進化に触れ始めました。2.5D TSVは、超高密度DRAMメモリやHBM(高帯域幅メモリ)と特定用途向けIC(ASIC)を同じICパッケージ内に実装できるようにするためのものです。今では、これらの回路アイテムは機能ブロックとしてSoCから切り離されています。スタンドアロンシリコンチップレットとしての中央処理装置(CPU)、GPU、汎用コンピューティングブロック、高速IOブロックなどがその例です。

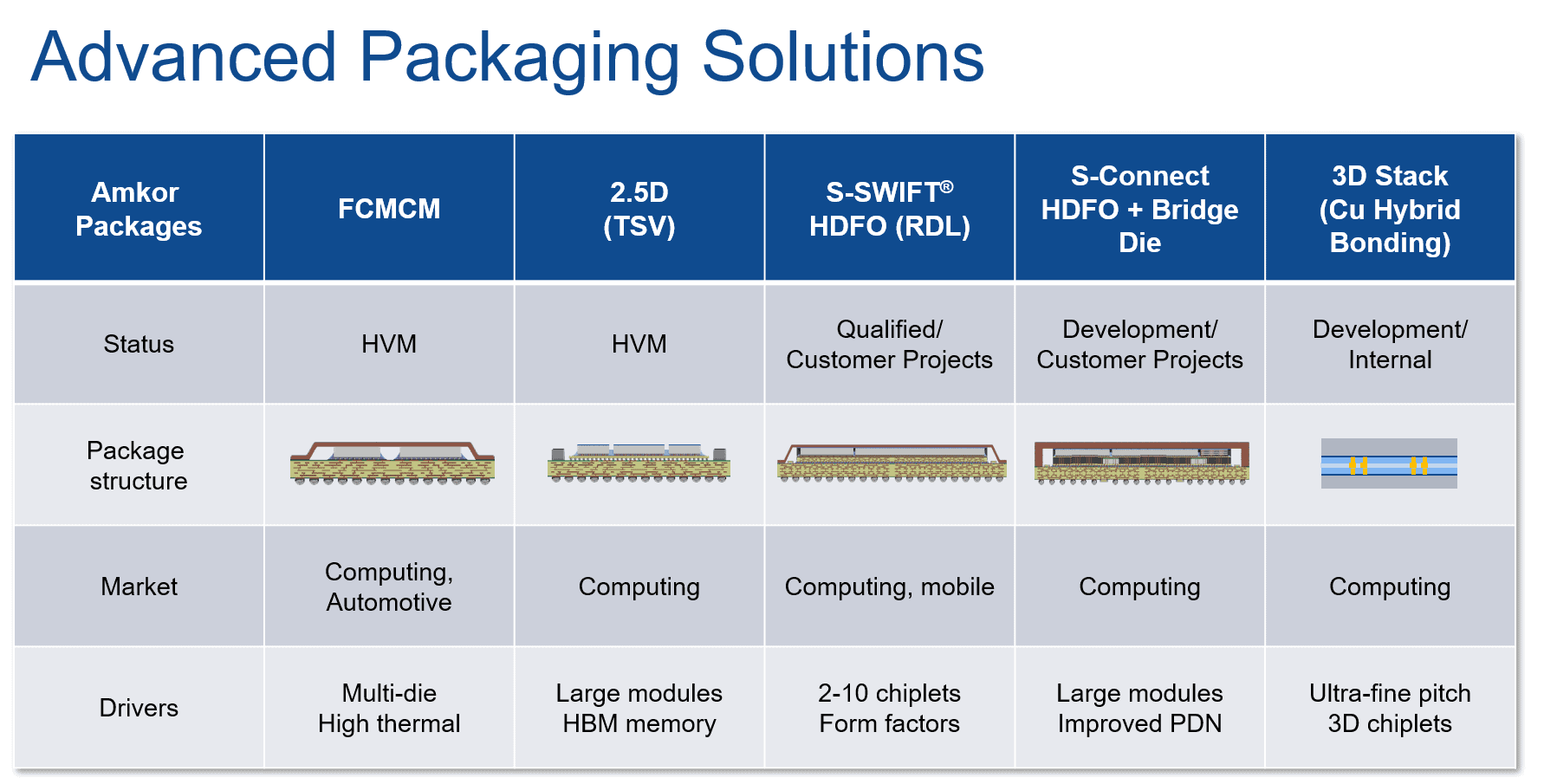

これらに対応するため、ロジックやメモリなど、数個または多数のチップを高性能なディスクリートチップの集合体に統合するいくつかの主要な技術が開発されてきました。これらの開発には、従来のパッケージサブストレートを利用した高密度マルチチップ製品、いわゆるマルチチップモジュール(MCM)フリップチップボールグリッドアレイ(FCBGA )や、2.5D TSVや高密度ファンアウト(HDFO)などの非常に精密な配列の構造が含まれます。サブストレートSWIFT(S-SWIFT)技術を使用した新しいチップレット統合は現在認定中です。S-SWIFT HDFOソリューションは、最小2µmのラインと2µmのスペース、および6層構造までの精密配線を可能にするものです。このモジュール製造技術は、過去3年間にわたって開発され、チップレットとHBMメモリの統合を現実的に可能にするようにアップグレードされてきました。S-ConnectはHDFOとブリッジを組み合わせたソリューションで、内部認定段階にあります。

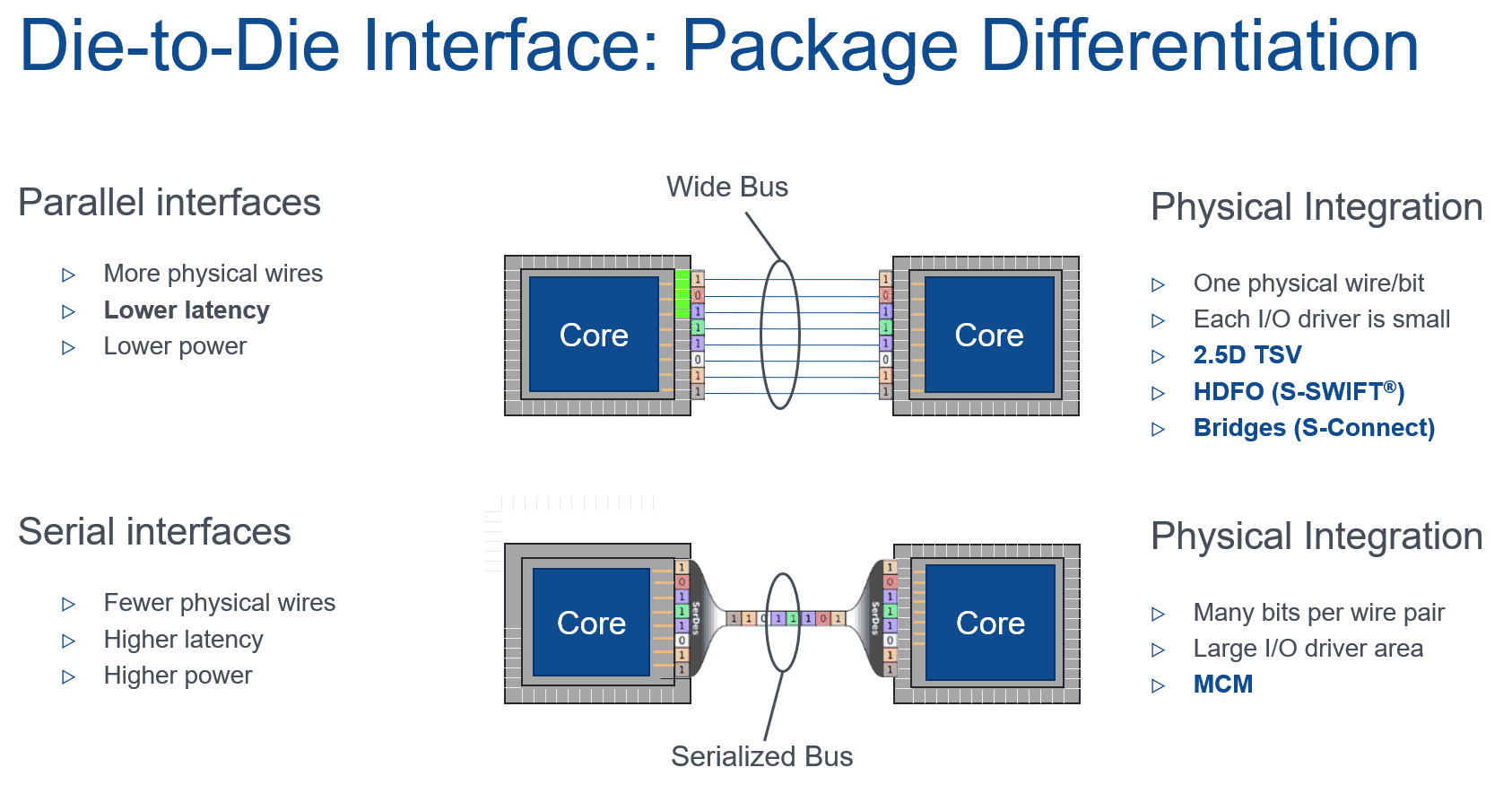

チップレットを使用するヘテロジニアス構造に実装するICパッケージング技術の選択は、チップレット間の通信インターフェイスに大きく影響されます(図1参照)。チップ間に100~1000のIOを備えた高速パラレルインターフェイスは多くの用途で好まれており、これにはシリコンインターポーザや高密度ファンアウト(HDFO S-SWIFT)を使用する2.5D TSVやブリッジ技術(S-Connect)などの高密度インターコネクトが必要です。

図1:チップ間インターフェイスの選択

S-SWIFTは、Cu細線フォトリソグラフィと有機誘電体を利用して、高密度信号配線をオンサイトで実現します。S-Connectでは、同等の高密度RDL技術の使用は控えめですが、高密度ブリッジを追加することでチップレット間の超高密度配線を支援しています。Cuハイブリッドボンディングによる超高密度垂直チップ間インターコネクトを用いた3Dチップスタッキングは、将来的には2D統合を補完するものとなるでしょう。

これらのパッケージング技術の未来は明るく、チップレットの2D統合用の新しい製品設計は昨年だけで4倍に増加しました。AmkorがヘテロジニアスICパッケージングロードマップにおける進歩を提供し続けているように、シリコンアーキテクチャの柔軟性向上、チップレットの再利用、市場投入期間の短縮、全体的なコスト削減は、パッケージング業界においてこのイノベーションを推進し続けています。

著者

Mike KellyはAmkor Technologyアドバンストパッケージ/テクノロジーインテグレーション担当バイスプレジデントです。Kellyは2005年にAmkorに入社し、EMIシールド、熱特性が強化されたパッケージ、センサー、および2.5D TSVと高密度ファンアウト(HDFO)を含む高密度MCMパッケージについて、パッケージ開発を主導してきました。エレクトロニクスおよびICパッケージの設計と製造に25年間携わり、ポリエステルフレキシブル回路から共晶フリップチップ、ICパッケージ設計、シグナルインテグリティに至るまで、幅広いプロジェクトを管理してきました。Kellyはこの分野で40以上の特許を取得しており、機械工学および化学工学の修士号を取得しています。