パッケージングの導電密度増加

ワイドバンドギャップ(WBG)半導体の技術により、パワーパッケージに新たな課題とチャンスが生まれました。炭化ケイ素(SiC)や窒化ガリウム(GaN)などの開発には、シリコン MOSFETと比較して高いフィギュア・オブ・メリット(FOM)があり、パワーエレクトロニクスの効率、出力電力および(または)スイッチング周波数範囲、動作温度範囲が拡大されました。

損失が低くなれば、既定サイズのパワーデバイスでも、より高い電力負荷をコントロールできます。例えば、GaN パワートランジスタを使用すると、パワーシステムはシリコンベースのシステムと比較して、サイズ、重量、および効率損失を1/4にすることができます。GaN 技術は、ワイヤレスシステムその他で低電力(50W)から中電力、さらには高電力レベルまでのシステムの課題を解決することができます。5G アプリケーションに採用されているため、高度な低電力から中電力のパッケージングに適しています。同様に、SiC には Si MOSFET を超える電力制御能力があり、多くのアプリケーション向けにアドバンストパッケージングが必要とされます。WBG デバイスのメリットや強みを活かすには、電力システム全体の価値を最大化する新たなパッケージングオプションが必要です。

今日のディスクリートパワーパッケージは、クリップ、ワイヤ、はんだのインターフェイスの電気的性能によって制限を受けます。一般的に、ディスクリートパッケージは、サイズや容積が大きくなると、より高い電力処理能力が得られるという相関関係の設計要件に従っています。しかしながら、これらのより効率的なトランジスタ技術は、同じサイズのパッケージでより多くの電力を処理したり、フォームファクタを大幅に縮小することが可能です。

旧来のパワーパッケージングで導電率を最大化するには、チップ設計に利用できるスペースの100%またはそれに近い割合で通電材へソースとドレインを接続する必要があります。従来、これはワイヤの数を増やす、ワイヤの直径を大きくする、またはソースかドレインに付けられたクリップのサイズを大きくするなどの方法で行われてきました。

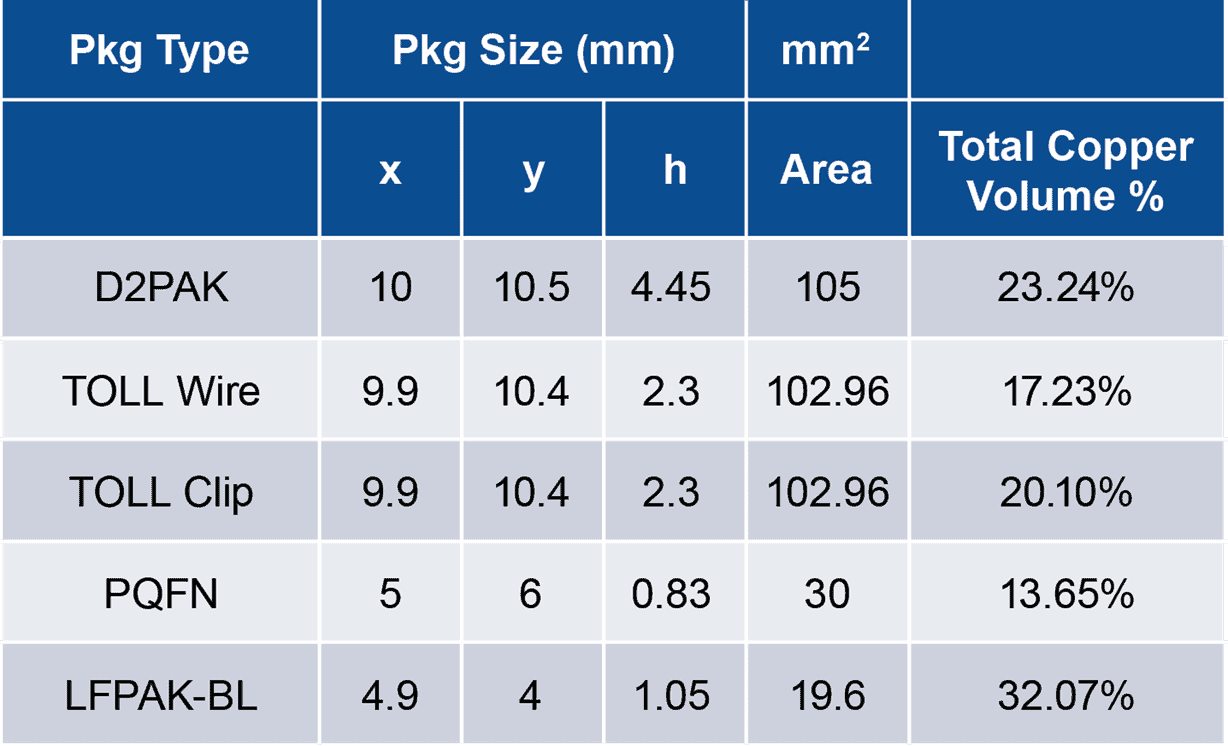

電力スペースでの機能性を大幅に改善するためには、3つのことが実現しなければなりません。第一に、ソースとドレインからの通電率を最大にする必要があります。第二に、熱的および電気的インターフェイスが完全になくされるか、長さ/厚さを大幅に縮小する必要があります。第三に、パッケージの導電性材料の密度を高める必要があります。下の図は、今日使用されている広範囲のパワー特有パッケージに対して導電性密度を検査したものです。

表 1. 既存パワーパッケージ比較データ

熱特性と電気特性の双方を最大化するには、パッケージ内にできるだけ多くの導電性材料を収容することが望ましいです。今日のほとんどのパワーパッケージングで、パッケージ中の導電性材料が 25% を超えることはまずありません(表 1 を参照)。

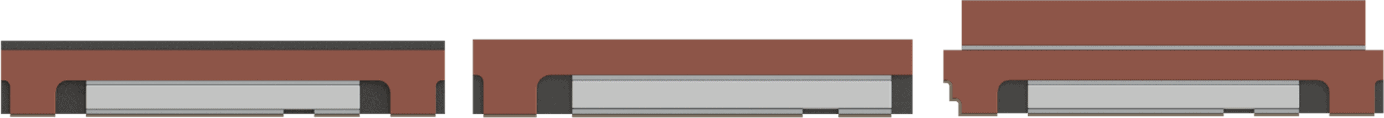

パッケージ内で導電性密度を最大にするには新しいパッケージフォーマットを創り出す必要があります。その一つのコンセプトが、Amkor が開発する PowerCSP™ です。PowerCSP 技術では、一般的に導電性密度が 40〜70% の範囲にあり、結果として旧来のパワーパッケージよりはるかに小さなフォームファクタで設計することができます。これは、クリップやワイヤの代わりに Cu サブストレートを使用しているからです。

図 2. PowerCSP™ 技術の実装による柔軟性と多数の構造オプション

図 2. PowerCSP™ 技術の実装による柔軟性と多数の構造オプション

PowerCSP 技術を活用し通電素子と放熱素子の両方の役を果たす Cu パッドに直接チップを接続することにより、チップがすべてのソースとドレイン領域を使用できるようになっています。これにより、パッケージは低い抵抗とインダクタンスを持つようになります。パッケージ全体の通電性密度が一つの要因となり、またソースとドレイン用にインターフェイス全体を使用することでシステムの潜在的損失を最小限に抑えます。

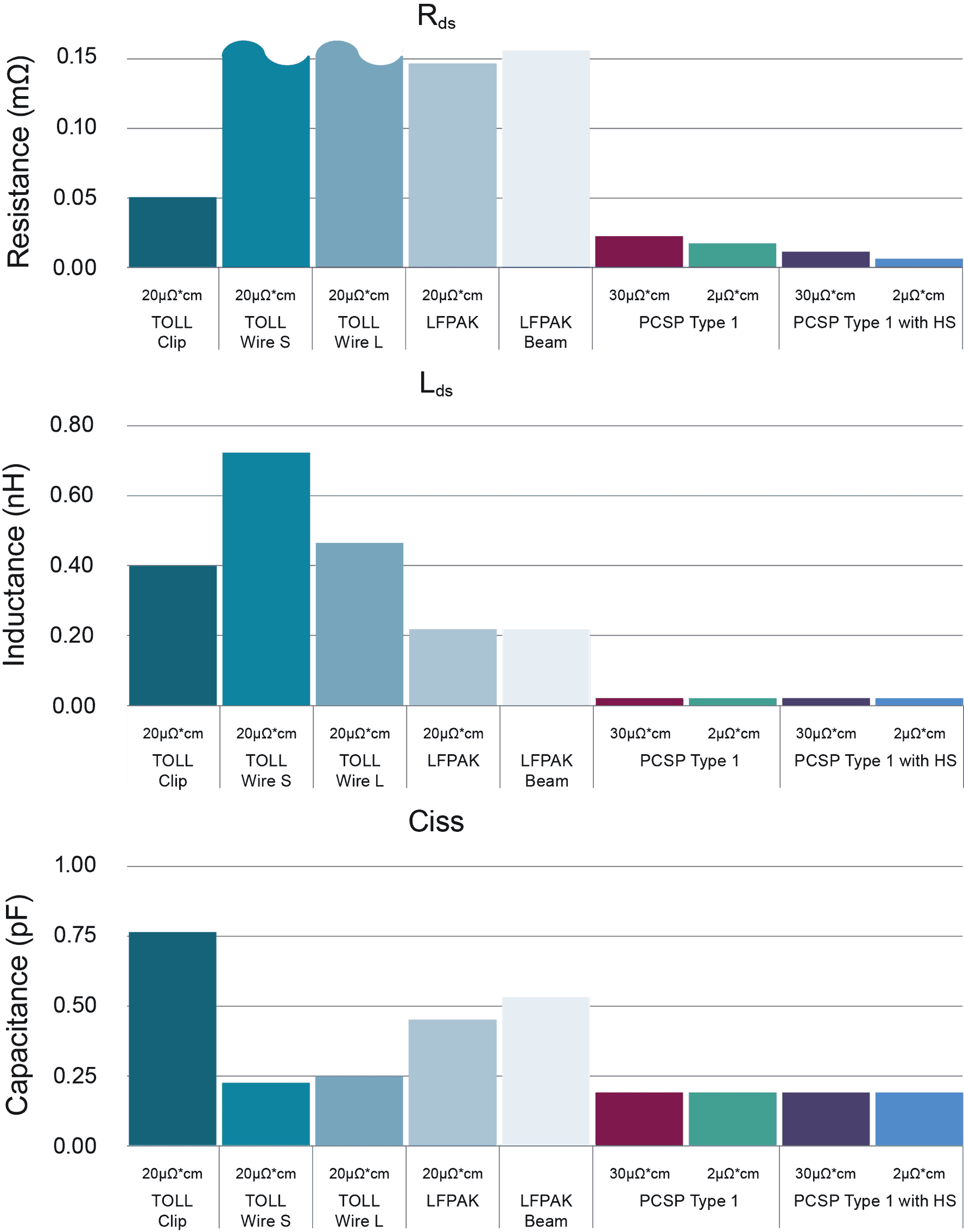

図 3. PowerCSP™ (PCSP) 設計の RDS、LDS、および Ciss と、

異なるバージョンの TOLL および LFPAK パッケージとの比較シミュレーション

他のパッケージのコンセプトは電力に注力して開発される場合がありますが、パッケージの導電性密度が重要な要因になります。Si、GaN または SiC のいずれでも、パッケージの導電性密度を増やすことで抵抗とインダクタンスを下げることや、パッケージ自体のフォームファクタを最終的に低減するメリットを享受することができます。パッケージの導電性密度を増やすことは、全体的な電力密度に対処するのに役立つだけでなく、Si と WBG デバイスが提供するすべてのことを活用できることにつながります。

著者

Shaun Bowers は、Amkor Technology Inc., Tempe, AZ のメインストリームアドバンストパッケージ担当VPです。Bowers は 2000年に Amkor へ入社し、現在は車載製品、リードフレームおよびパワーパッケージング事業部門の責任者です。彼は以前は技術プログラムマネジメント、販売と顧客サービスの職務にも携わりました。Amkor 入社前は、Johnson Matthey Electronics および Honeywell Electronic Materials に勤めていました。Bowers は Gonzaga 大学の機械エンジニアリングの学位取得。