S-SWIFT™技術によるICパッケージングの変革

ファンアウトと基板の融合

特にAI、HPC、データセンターにおける高性能デバイスの需要は、進化し続ける集積回路技術の状況において劇的に急増しています。この需要はコロナ禍によってさらに加速し、シリコン技術の限界を押し広げています。AmkorのS-SWIFT™は、これらの課題に対処し、ICパッケージング業界に革命を起こすために設計された画期的なパッケージングソリューションです。

高度なパッケージングソリューションの必要性

現在は3nmの世界で業界がシリコン技術ノードの最小化に努めるにつれて、関連するコストと開発時間は急増しています。ノードサイズが小さいほど、欠陥のリスクが高くなり、ウェハーの歩留まりが低下します。チップレット技術はこれらの制限に対する実用的なソリューションとして登場し、コアブロックのより小さなダイへの分離を可能にし、これによりウェハーの歩留まりを向上させ、設計コストを削減します。しかし、これらのヘテロジニアスブロックダイを相互接続するには、高度なICパッケージング技術が必要です。

ICパッケージングの進化

従来、マルチチップモジュール(MCM)フリップチップボールグリッドアレイ(FCBGA)パッケージは、ラミネート基板上のマルチチップのヘテロジニアスインターフェースに使用されてきました。ただし、このアプローチは、基板の電気経路が長いため、高度なノードICには不十分です。2.5D Through Silicon Via(TSV)テクノロジーの導入により、電気経路が短縮されましたが、高周波アプリケーションでの性能の問題によって制限されました。これにより、高密度ファンアウト(HDFO)インターフェースが開発され、シリコンと無機誘電体を排除し、有機誘電体が採用されました。

S-SWIFT:ゲームチェンジャー

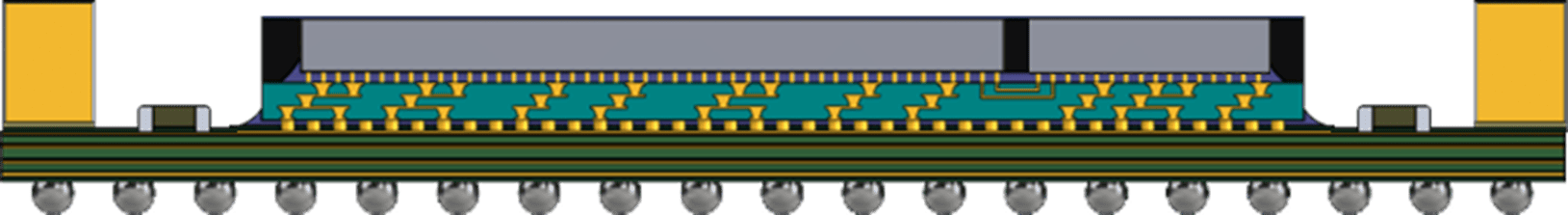

Amkor TechnologyのS-SWIFT(Substrate Silicon Wafer Integrated Fan-out Technology)パッケージは、HDFOの世界で際立ち、高密度インターポーザーとのヘテロジニアス統合のためのより高い帯域幅とダイ間相互接続を提供します。S-SWIFTの手法は、ファインピッチ、μバンプインターフェース、熱アセンブリ中の正確な反り制御、キャピラリーアンダーフィル、オーバーモールド技術、金型側のバンピングプロセスなど、いくつかの重要な設計の側面に対応しています。

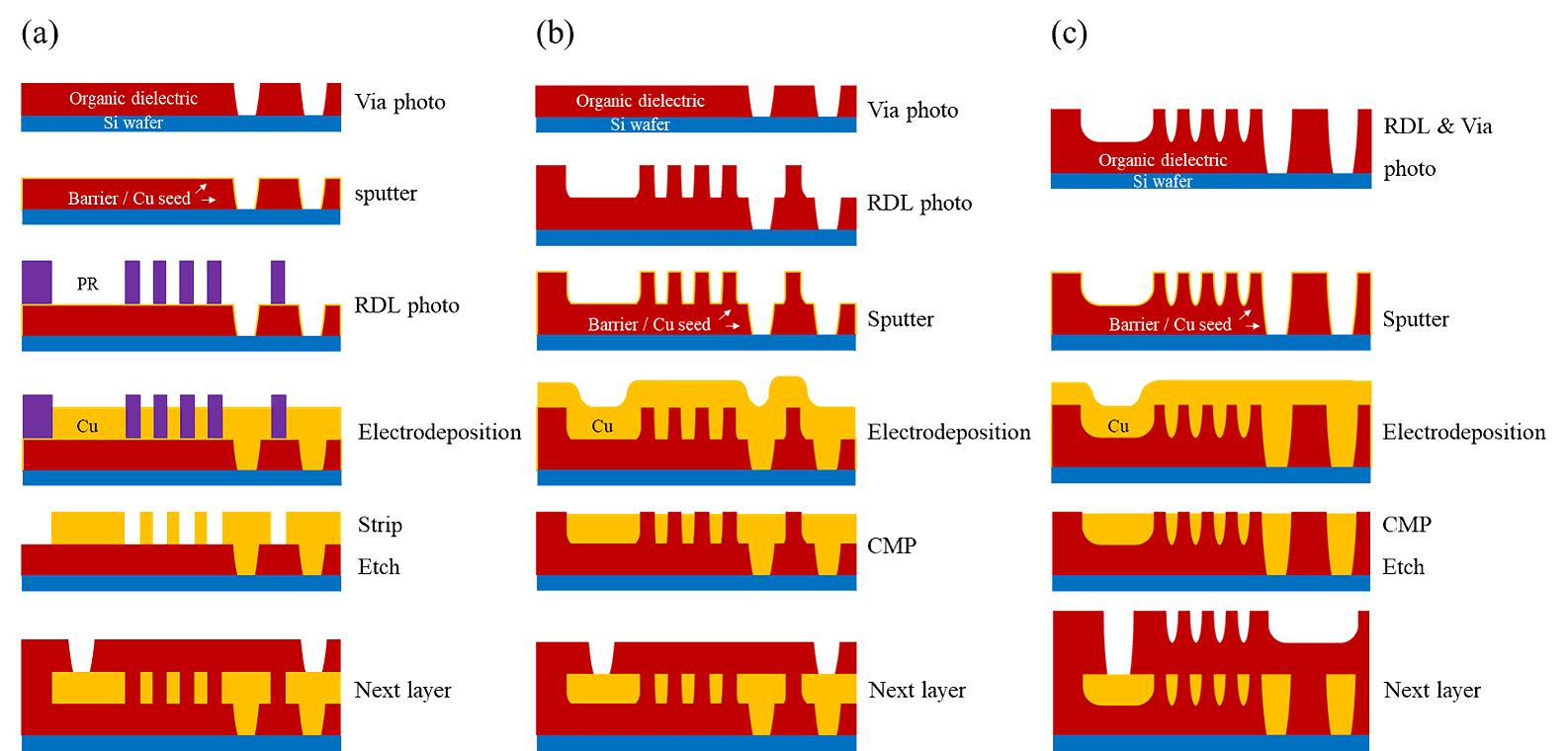

S-SWIFTのコア技術の一つが、高密度再分配層(RDL)技術です。HDFOパッケージでは、RDLがチップ間インターフェースを提供し、より小さなノードサイズブロックでチップを相互接続するには、より高密度のRDLが不可欠です。RDL製造では、セミアディティブプロセス(SAP)が主流の技術ですが、ファインピッチの特徴を定義する上で課題に直面しています。これらの問題を克服するために、有機誘電体にRDLを埋め込むデュアルダマスカスプロセスを提案し、シード層のアンダーカット問題を防ぎます。

図1: S-SWIFT™

Embedded Trace RDL(ETR)プロセス

Embedded Trace RDL(ETR)プロセスは、RDL製造における大きな進歩です。これは、エッチングプロセスを行わずに誘電体層にトレースを埋め込むもので、シード層のアンダーカットやサイドウォールエッチングの問題などの課題に対処します。ETRプロセスのデュアルダマシン銅(Cu)構造は、滑らかなCu表面が電子散乱の影響を受けにくいため、高周波信号パス特性に利点があります。

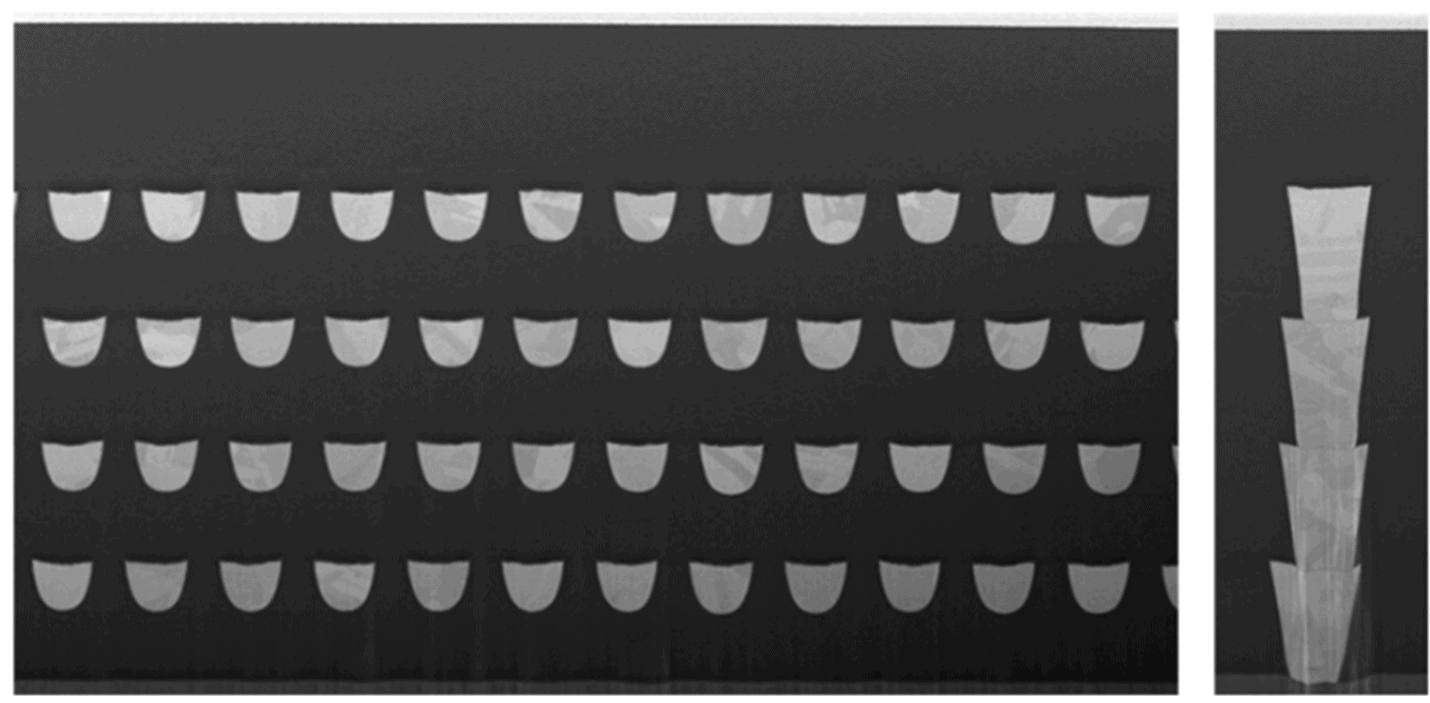

また、ETRはRDLの製造プロセスを簡素化し、現在のデュアルダマシン法と比較してステップ数を40%、SAPと比較して33%削減します。このプロセスステップの削減は、コストの削減と効率の向上につながります。ETRプロセスは、優れたパターニング能力を実証し、2/1μmのライン/スペース寸法とさまざまなビアサイズのトレンチパターンを達成しています。

図2:(a)半付加プロセス(SAP)、(b)デュアルダマシンプロセス、(c)新しい組み込みトレースRDLプロセスによるRDLプロセスフローの概略図。

図3:ETRプロセスにより形成された2/1μmの線幅/間隔と2μmのスタックビアを持つ4層RDLの断面画像

信頼性とパフォーマンス

S-SWIFTパッケージのETR構造の信頼性は徹底的にテストされています。ETRの3つの面を囲むシード層はバリアとして機能し、Cuイオンの移動を防ぎ、電流、熱、湿度の条件下での信頼性を確保します。ETR付きのS-SWIFTパッケージは、水分浸漬、温度サイクル、偏りのない高加速ストレステスト、高温保存テストなど、業界標準の信頼性テストに合格しています。

結論

Amkor TechnologyのトレースRDLが組み込まれたS-SWIFTパッケージングは、ICパッケージング技術における大きな飛躍を表しています。S-SWIFTは、従来のパッケージング方法の限界に対処し、信頼性の高い高性能ソリューションを提供することで、AI、HPC、データセンターアプリケーションの高まる需要に対応する態勢を整えています。業界がシリコン技術の限界を押し広げ続ける中、S-SWIFTのようなイノベーションは、ハイパフォーマンスコンピューティングの未来を形作る上で重要な役割を果たすでしょう。詳細についてはAmkor.com/s-swiftをご覧ください。