S-SWIFTは革新的な新パッケージング技術です

Substrate-SWIFT(S-SWIFT)テクノロジーは、Silicon Wafer Integrated Fan-Out(基板上)とも呼ばれ、高度なパッケージングの世界に革命をもたらしています。I/Oと回路の密度を向上させながらフットプリントとプロファイルを縮小するS-SWIFTはシングルダイとマルチダイの両方のアプリケーションに最適なソリューションであり、モバイルおよびネットワーキングデバイスにおけるIC統合の高度化に対する需要の高まりに完全に対応しています。

S-SWIFTは、ヘテロジニアスICパッケージのゲームチェンジャーとして際立っており、複数のチップレットとメモリの高性能でコスト効率の高い統合を可能にします。この技術は、I/Oと回路の密度を向上させるだけでなく、高度な3D構造への道を開くもので、次世代のモバイルおよびネットワーキングアプリケーションにとって不可欠なものとなっています。S-SWIFT技術は、大きなパッケージサイズと高いI/O密度(>1000)を必要とするアプリケーションに最適です。

ファンアウトと基板の融合

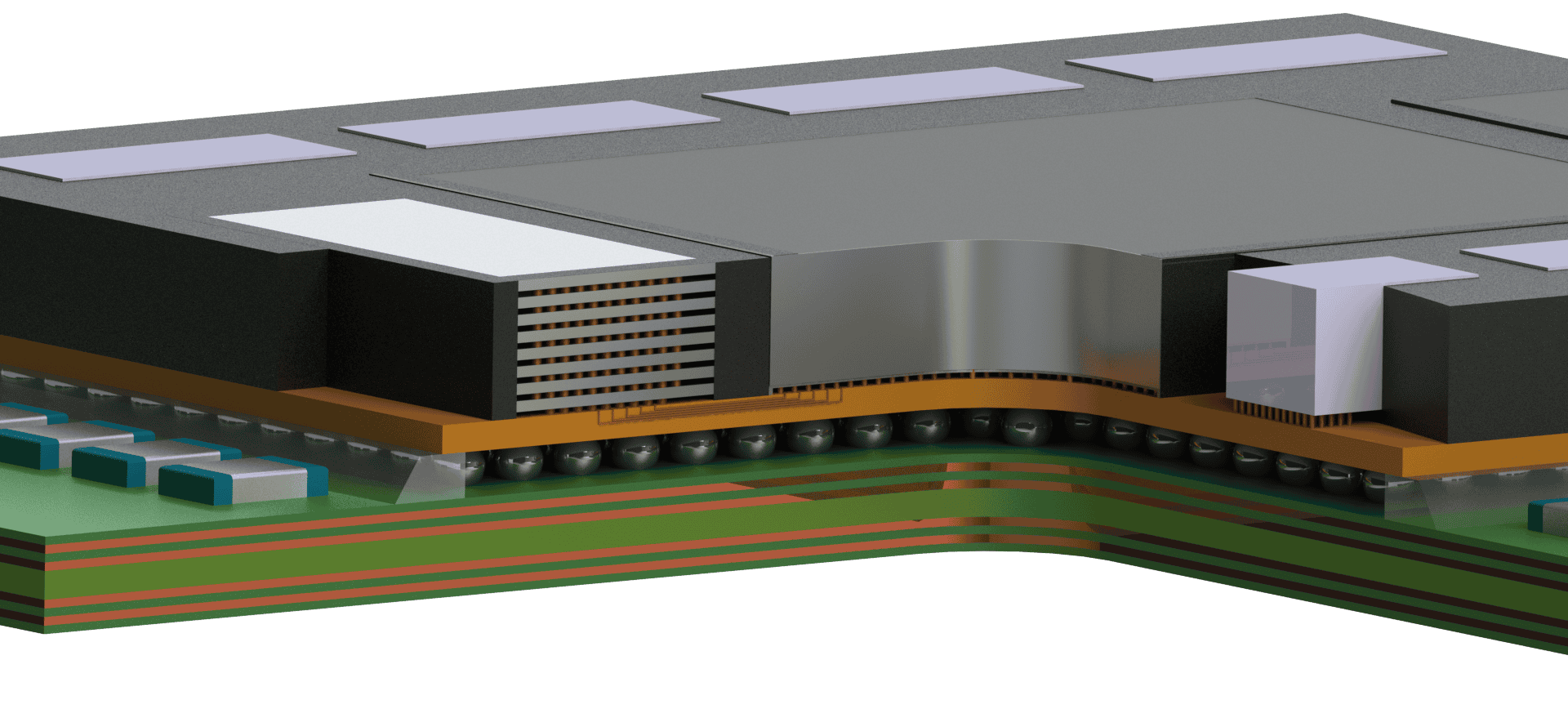

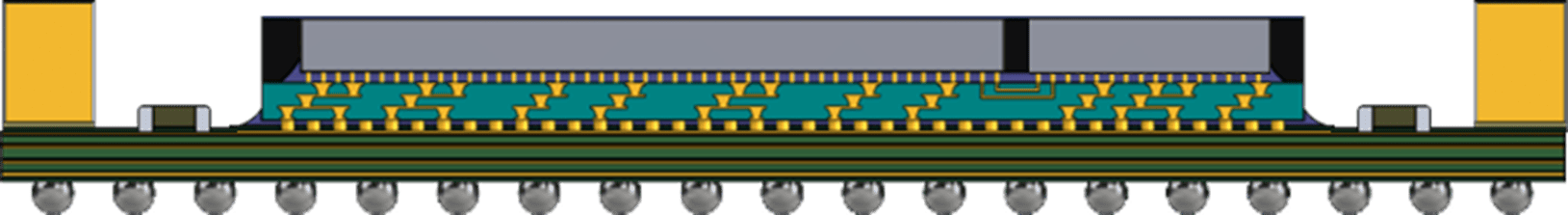

2.5D TSVの革新的な代替品であるS-SWIFTは、チップ性能を向上させ、コストを削減するファンアウトパッケージです。S-SWIFTは、ピン数の多いボールグリッドアレイ(BGA)基板にチップをフリップチップで実装し、D2D(Die-to-Die)相互接続を短くするためのRDL(Redistribution Layer)を組み込むことで、ファンアウトパッケージ全体を1つのダイとして扱います。このインテリジェントな設計はBGA基板に実装され、従来の2.5D Through Silicon Via(TSV)技術に代わる費用対効果の高い選択肢を提供します。

S-SWIFTの主な特徴は、複数のチップ間のD2D相互接続を短縮できるRDLにあります。この設計では、ファンアウトパッケージ全体を1つのダイとして扱い、BGA基板に実装します。これらの高度な機能を統合することにより、S-SWIFTは従来の2.5D TSV技術に代わる費用対効果の高い選択肢を提供します。

パッケージ構造

- ピン数の多いBGA基板に実装されたファンアウトパッケージフリップチップ

- RDLは複数のチップ間のD2D相互接続を短縮

チップの統合

- 複数のチップレットを1つのパッケージに統合

- チップレットはASICやHBMなどさまざまな機能ユニット化が可能

インターポーザーレス設計

- インターポーザーの必要性を排除し、複雑さとコストを削減

電気的性能

- D2D接続が短く、優れた電気的性能を提供

- 挿入損失の低減、インピーダンス制御の改善、反りの低減が特長

高I/O密度

- 高いI/Oカウント(1000超)に対応

- 大型パッケージサイズやネットワーキング/サーバーアプリケーションに最適

- 費用対効果:インターポーザーの必要性を排除し、パッケージコストを削減

- 電気的性能:より優れたインピーダンス制御、挿入損失の低減、反りの低減で電気的性能が向上

- 高いI/Oカウント:1000を超えるI/Oを備えたパッケージをサポートするため、ネットワーキングおよびサーバーアプリケーションに最適

- 市場投入までの時間:既存のファンアウト/フリップチップ技術を活用して市場投入までの時間を短縮

S-SWIFT™技術は2.5Dに比べて低コストで、パッケージが薄く、挿入損失が小さく、インピーダンス制御が改善され、反りが少ないため、優れた電気的性能が得られます。これらの利点により、S-SWIFTは関連アプリケーションにとって魅力的な選択肢となっています。

主な用途は次のとおりです。

- ハイパフォーマンスコンピューティング(HPC):重要な相互接続を効率的に実現することでHPCアプリケーションを強化

- ネットワーキングおよびサーバーアプリケーション:I/O密度が高いS-SWIFTはネットワーキングやサーバーのニーズに最適

- 人工知能(AI): 優れた電気的性能と高速で低レイテンシのチップ間インターコネクトは大量のメモリと計算能力を必要とするAI用途に最適

- ASICおよびHBM:S-SWIFTのチップラスト技術はASICとHBMのパッケージングに最適

ご質問やお問合せはこちらまで

以下の「リクエスト」をクリックしてご連絡ください